Trends and Requirements for Network Processor SoC tools MP SoC School, July 2002

Pierre Paulin, Director SoC Platform Automation Technologies STMicroelectronics, Ottawa, Canada

## Outline

- Network Processors

- ≫Why?

- ➤High performance: How?

- >NPU tools survey

- □ StepNP<sup>TM</sup> Research NPU Platform

- Parallel processor architecture

- Router applications

- SoC tools and methods

- R&D Needs Outlook

- >>Which platform, which SoC tools?

#### Why are NPU's Interesting?

- Key component of emerging intelligent high-bandwidth optical network

- Commercial perspectives

- First real industrial parallel processing application

- Cost-effective & useable parallelism

- Perfect driver for next generation SoC tools

- > Embedded software & System-level design tools

- > Multi-processor tools

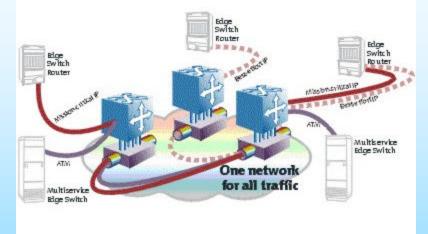

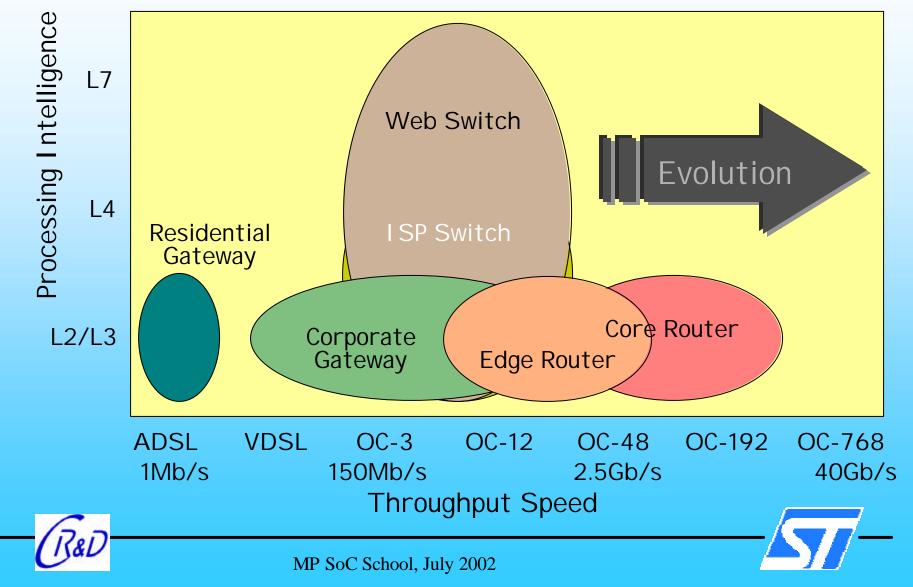

#### **Router/Switch Space (Today)**

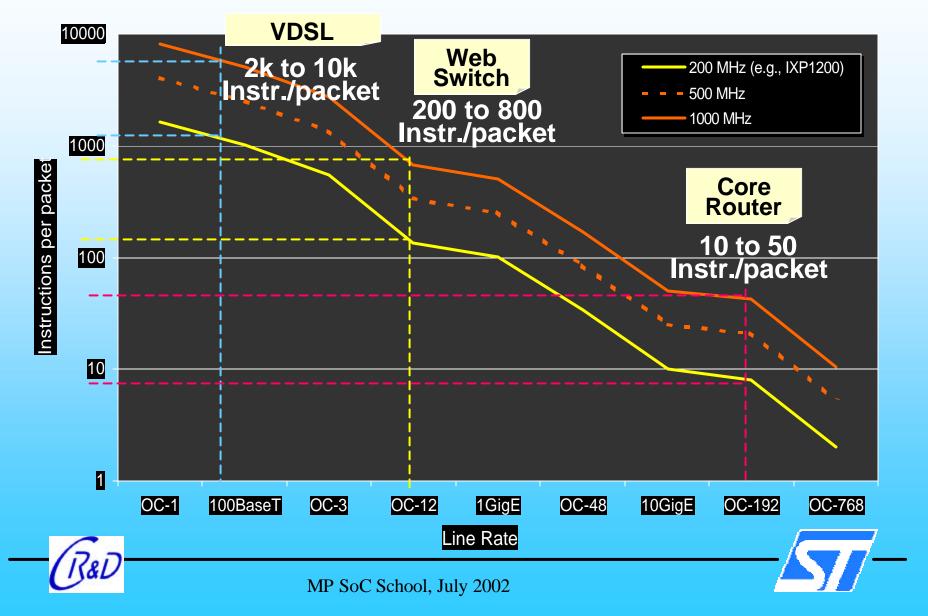

#### **NPU Instructions / Packet**

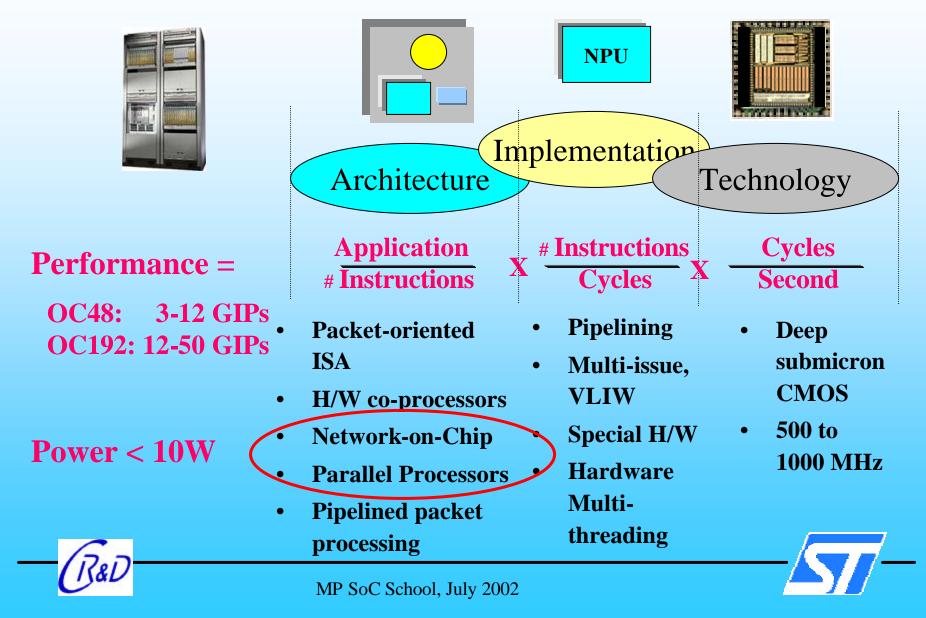

#### **Enabling High Performance**

# **NPU Tools Survey**

Common NPUs at 2.5 Gb/s and 10 Gb/s (Info from company public web sites, updated Feb. 2002)

| <u>NPU</u><br>(2.5 Gb)       | HLL                                  | <u>Debug</u>             | <u>ISS</u> | <u>System</u><br><u>Model</u>           | <u>Lib</u>           | <u>Other</u>                                |

|------------------------------|--------------------------------------|--------------------------|------------|-----------------------------------------|----------------------|---------------------------------------------|

| IBM<br>PowerNP               | C: ppc only<br>VxWorks               | sim,oce<br>Fr inject     | Yes        | Yes<br>Tcl/Tk I/F                       | Yes                  | Perf. analysis<br>Ref. Board                |

| Agere<br>Payload+            | FPL, C<br>VxWorks                    | Yes<br>IDE               | Yes        | Throughput<br>modelling                 | Yes                  | Packet gen.<br>Ref. Board                   |

| Motorola<br>C-5              | GCC<br>VxWorks                       | GDB                      | Yes        | Perf. Model<br>(250X HDL)               | C-ware               | Perf. analysis<br>Packet gen.               |

| Intel<br>IXP1200             | ueC, symb.<br>macro-asm<br>NPOS, OS9 | Cycle-<br>acc dbg<br>IDE | Yes        | Cycle-acc.<br>FL-API                    | Teja<br>uWare<br>ACE | Perf. analysis<br>Packet gen.               |

| Conexant<br>Mxt4400          | GCC<br>(2001?)                       | Yes                      | Yes        | Cycle-acc.                              | Yes                  | Perf. analysis<br>Packet gen.               |

| Sitera<br>IQ2000             |                                      | GDB<br>Sim,<br>jtag oce  | Yes        | Functional,<br>HDL cosim,<br>Tcl/Tk I/F | Yes                  | Perf. analysis<br>Packet gen.<br>Ref. board |

| ReD MP SoC School, July 2002 |                                      |                          |            |                                         |                      |                                             |

| <u>NPU</u><br>(10 Gb)    | HLL                              | <u>Debug</u>              | ISS          | <u>System</u><br><u>Model</u> | Lib | <u>Other</u>                                |

|--------------------------|----------------------------------|---------------------------|--------------|-------------------------------|-----|---------------------------------------------|

| Lexra<br>Netvortex       | CC<br>VRTX OS                    | m-p/m-thr<br>IDE          | Yes          | Cycle-based                   |     | OCE (JTAG)                                  |

| AMCC /<br>MMC<br>nP7510  | m-p CC<br>h/w OS<br>VxWorks      | XRay<br>IDE:<br>WindRiver | Yes          |                               | Yes | OCE (JTAG)<br>Ref board                     |

| Clear<br>Speed           | m-p CC                           | m-p dbug<br>IDE           | Yes          | Yes                           | Yes | Perf. analysis                              |

| Si Access                | iAtom CC                         | m-p/m-thr<br>IDE          | Yes<br>(C++) | Cycle-based<br>(C++), API     | Yes | Perf. analysis<br>Packet gen.               |

| Cisco<br>Toaster         | CC (CCC)<br>Cisco IOS            | Yes                       | Yes          | Cycle-based                   | Yes |                                             |

| Agere<br>Payload+        | FPL, ASL<br>VxWorks,<br>Linux OS | Yes,<br>IDE               | Yes          | Cycle-based,<br>C/Java API's  | Yes | Perf. analysis<br>Packet gen.<br>Ref. Board |

| MP SoC School, July 2002 |                                  |                           |              |                               |     | -57-                                        |

#### **NPU Tools Summary**

|                                  | <u>2.5G</u> | <u>10G</u> |

|----------------------------------|-------------|------------|

|                                  | 6/6         | 6/6        |

| Source-level debugger            | 4/6         | 6/6        |

| System-model (cycle-based)       | 4/6         | 4/6        |

| O/S support (mostly on ctrl proc | ) 4/6       | 4/6        |

| Packet generation                | 5/6         | 2/6        |

| HLL compiler                     | 4/6         | 6/6        |

| Performance analysis             | 4/6         | <u>3/6</u> |

| Multi-processor compilation      | <u>0/6</u>  | <u>2/6</u> |

## Outline

Network Processors

- □ <u>StepNP<sup>™</sup> Research NPU Platform</u>

- >Overview

- ➤Parallel processor architecture

- Router application software

- SoC tools and methods

- R&D Needs Outlook

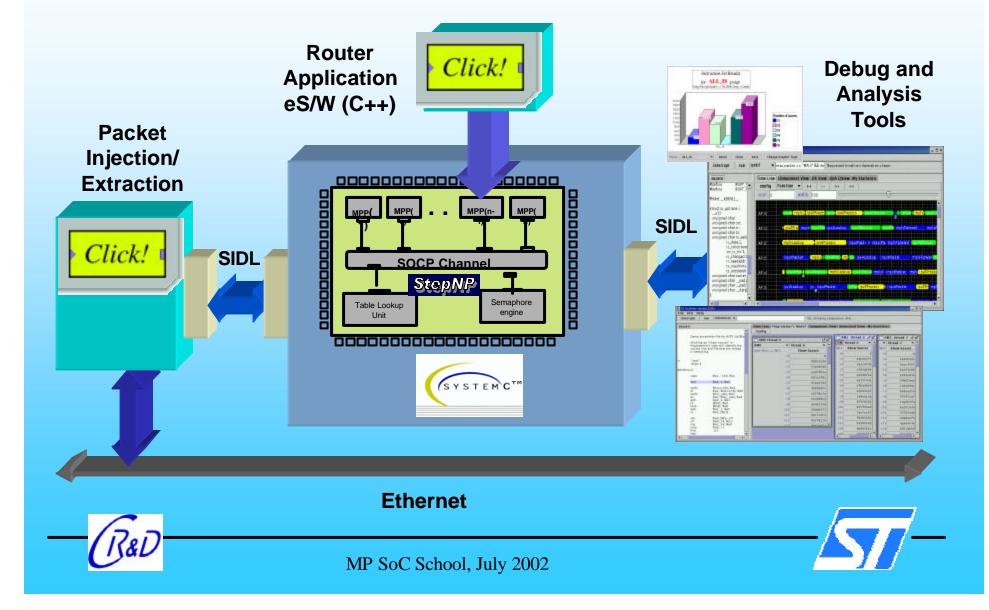

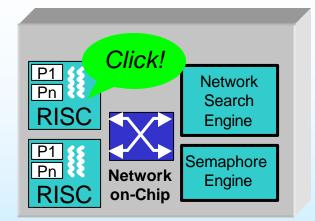

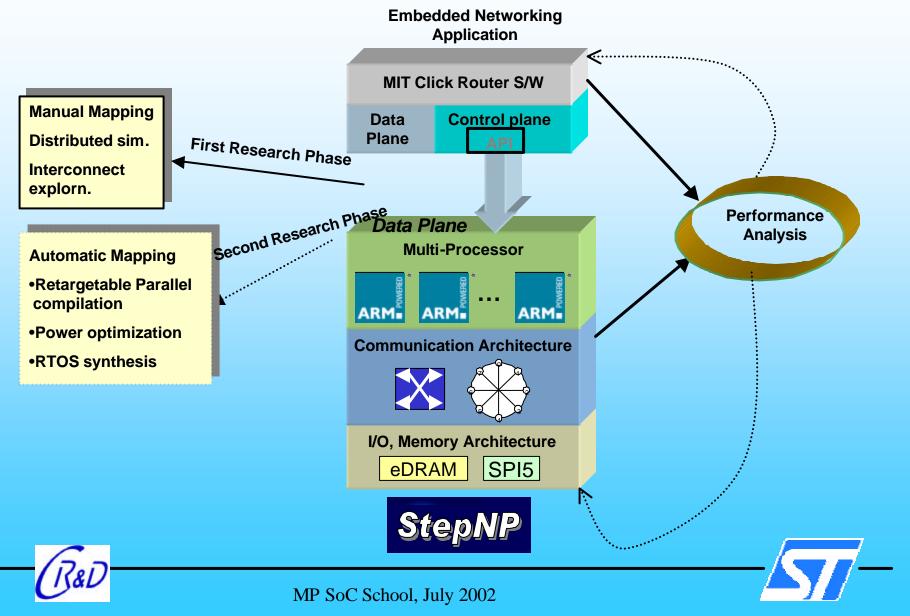

## **StepNP<sup>TM</sup>** Reference Platform

System-level Telecom **Exploratory Platform for** Network Processing For Academic Partners Canada, International **For Commercial CAD partners** For ST system design, embedded systems and platform automation R&D teams > Challenging internal driver For ST customers Reference platform for communication IP Tool driver for real NPU's

MP SoC School, July 2002

#### STMicroelectronics StepNP<sup>TM</sup> Reference Platform

## **StepNP<sup>TM</sup>** Reference Platform

Tools for S/W

productivity

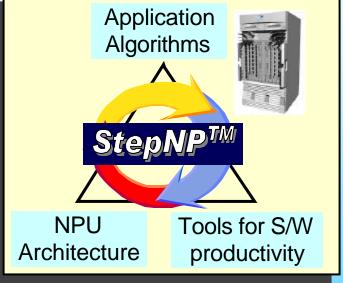

Application S/W Application MIT Click modular router Algorithms Architecture > Processor array: ARM, Tensilica, StepNP PowerPC, DLX > Interconnect: NPU Split-transaction bus, Architecture Octagon, Spin, Amba, ring, crossbar Network search engine, co-proc., semaphore engine, memory, I/O Tools ST NPU SoC tools prototype MP SoC School, July 2002

## **StepNP<sup>™</sup> Outline**

What is StepNP<sup>™</sup>?

Hardware Architecture

Multi-threaded processors

Interconnect

Routing software

Tools and Methodologies

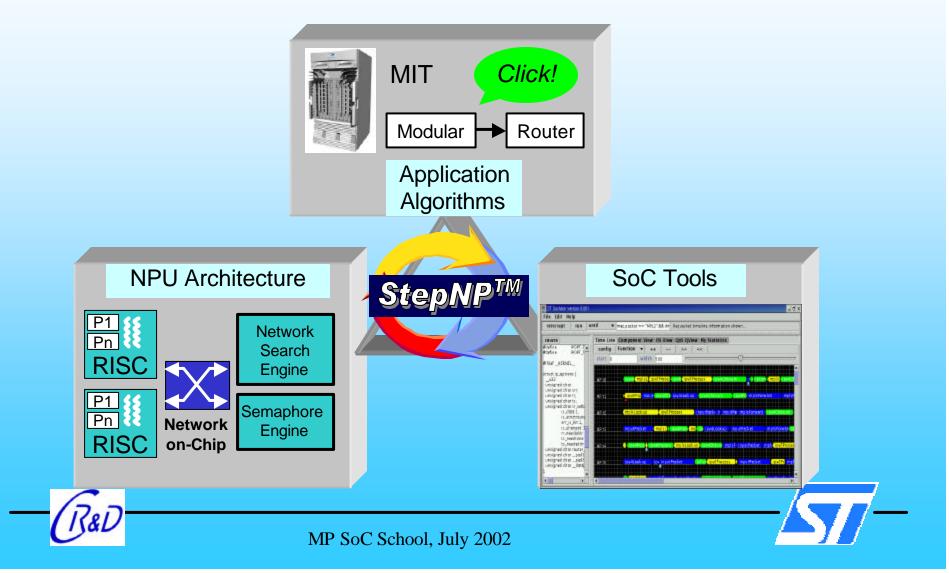

## **StepNP<sup>TM</sup> H/W Architecture**

#### **H/W Multi-threaded Processor**

# Principal approach : Block interleaving technique: The instructions of a thread are executed successively until an event occurs that may cause latency (ie: read memory data)

## **StepNP<sup>TM</sup> Reference Processor**

Hardware multi-threaded processor >> Standard approach for network processors Hide latency via zero overhead thread context switch Configurable number of hardware threads per processor (default 8) > Configurable pipeline depth (default 4) Each thread executes functional instruction set (e.g. ARM, PowerPC) StepNP primary focus not on instruction set of NPU SystemC cycle-accurate model >> Encapsulation of functional ISS (ARM, DLX, PowerPC, etc.)

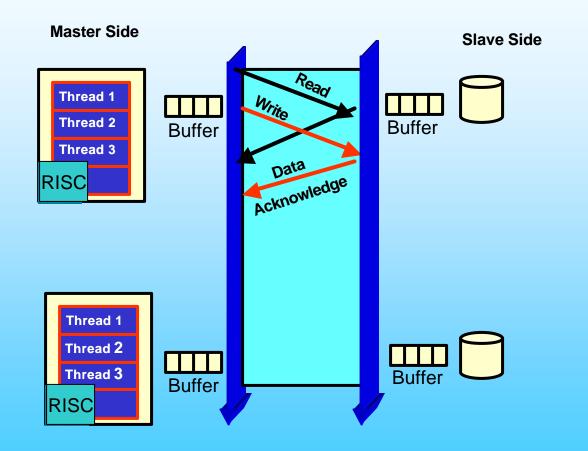

## **StepNP<sup>TM</sup> Interconnect Models**

A general framework for interconnects, to allow architecture exploration

- Multi-level modelling

- Transaction-level to cycle-accurate models

- Various interconnect architectures

- Split-transaction bus, SPIN (Paris LIP6), Octagon (ST), ring, crossbar, Amba bus, Sonics

- Currently developing various channel implementations +> Functional, transactional, cycle-based

- Distributed simulation is another form of implementation

#### **Split Transaction Bus Model**

MP SoC School, July 2002

## **StepNP<sup>™</sup> Outline**

What is StepNP<sup>™</sup>?

Hardware Architecture

>Multi-threaded processors

>Interconnect **Routing software**Tools and Methodologies

## **StepNP<sup>TM</sup> Routing Software**

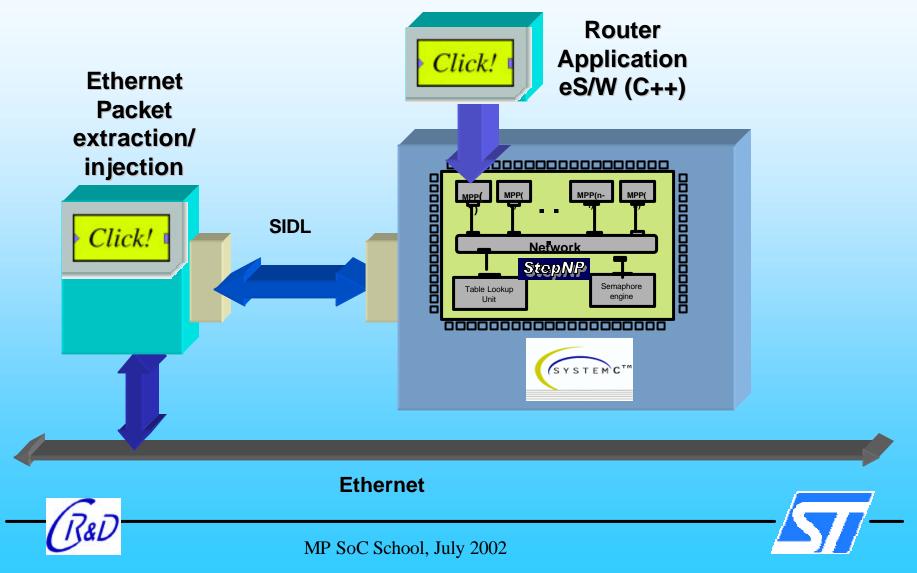

Uses the MIT Click router software MIT http://www.pdos.lcs.mit.edu/click Modular Click is >> Available under open-source license > modular, flexible, configurable Fine-grained modularity of Click allows efficient parallel execution. **Router configurations expressed in a simple** language

## **StepNP<sup>TM</sup> Routing Application**

- □ A simple network translation (NAT) application

- Easy to set up testbench environment

- Emulates a "virtual host", by capturing packets off real ethernet, performs NAT algorithms, and injects back on to ethernet.

- Can set up real network applications (telnet or web browsing) with the virtual host, and watch StepNP simulator processing packets.

#### Application and Architecture Testbench

## **StepNP<sup>™</sup> Outline**

□ What is StepNP<sup>™</sup>?

□ Hardware Architecture

> Multi-threaded processors

> Interconnect

□ Routing software

□ Tools and Methodologies

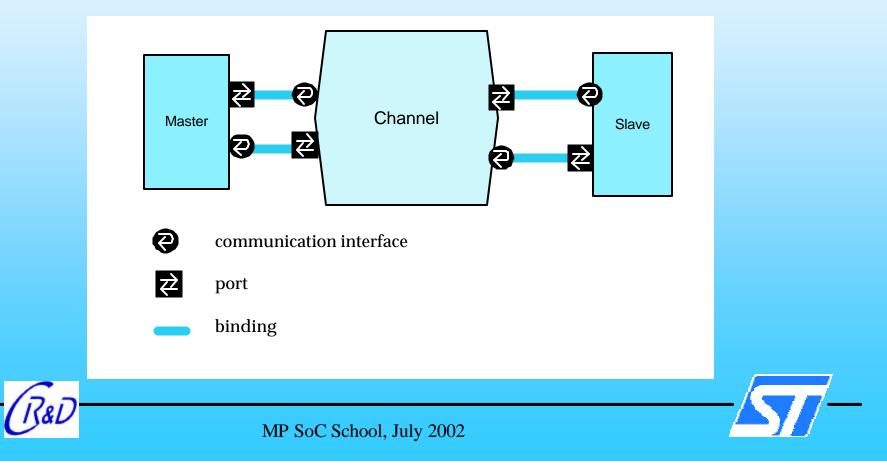

#### SOCP Transaction-Level Model Channel Interface

#### Based on OCP (VCI) semantics

Transaction-level interface (no pins, signals, clk)

## **SOCP Channel Interface (contd.)**

Simulation speed results for functional **SOCP** implementation >Unix Ultra80 (450 MHz) 250 KHz (to 1.2 MHz) ► Linux PC (800 MHz) 1.5 MHz (to 1.5 MHz) Distributed simulation using SOCP > Special SOCP channel uses TCP/IP, SystemC modules assigned manually to W/S Lower bound on simulation speed (if limited only by TCP/IP communication) ⇒30 KHz over TCP/IP 100Mb Ethernet Exploring Myrinet implementation (U. of Montreal)

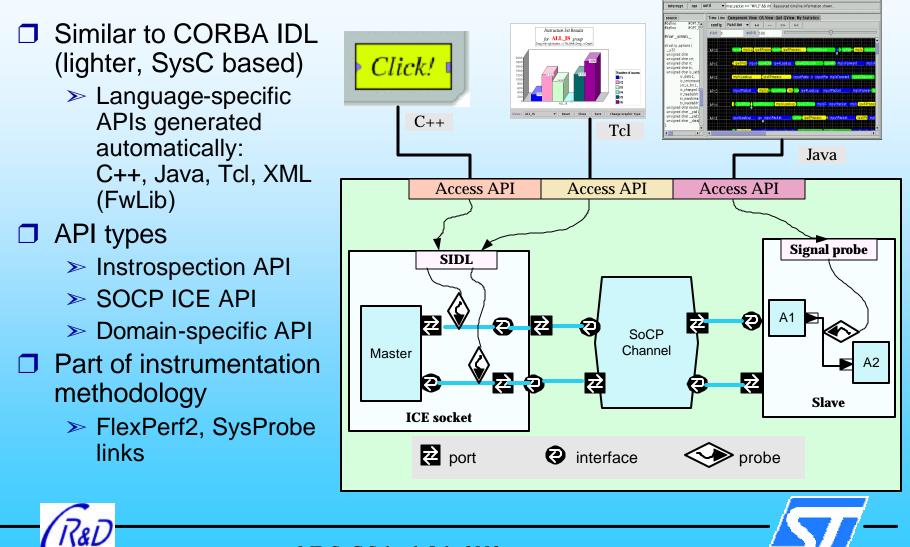

## SIDL (SystemC IDL)

MP SoC School, July 2002

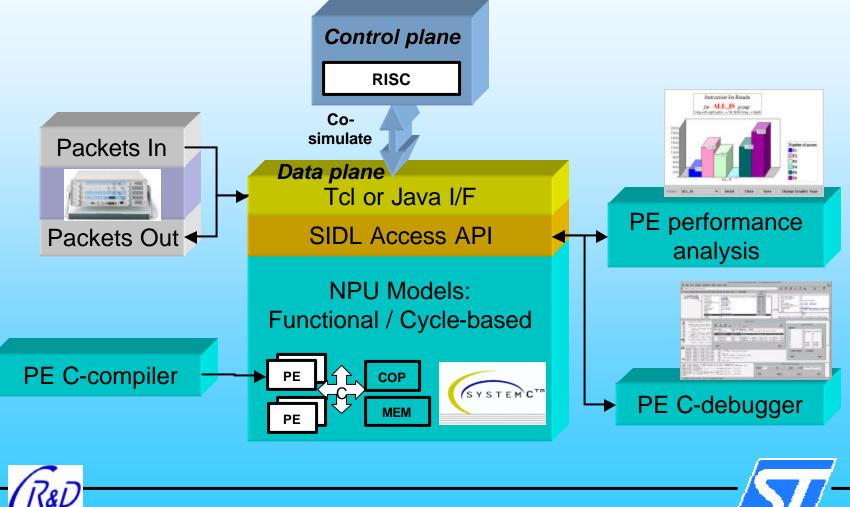

#### **NPU eS/W Tools**

MP SoC School, July 2002

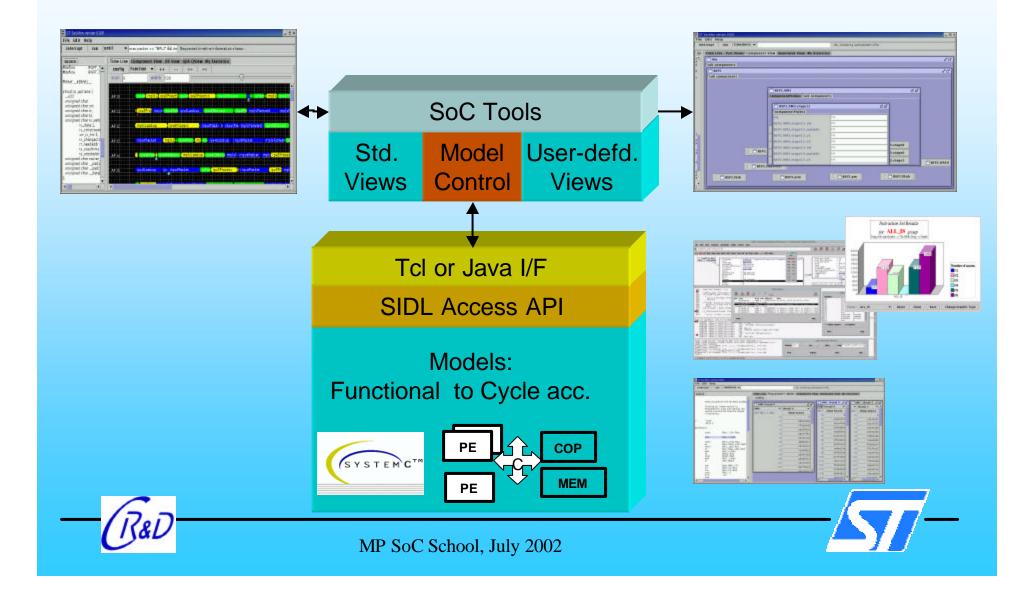

#### **StepNP<sup>TM</sup> Tool Platform**

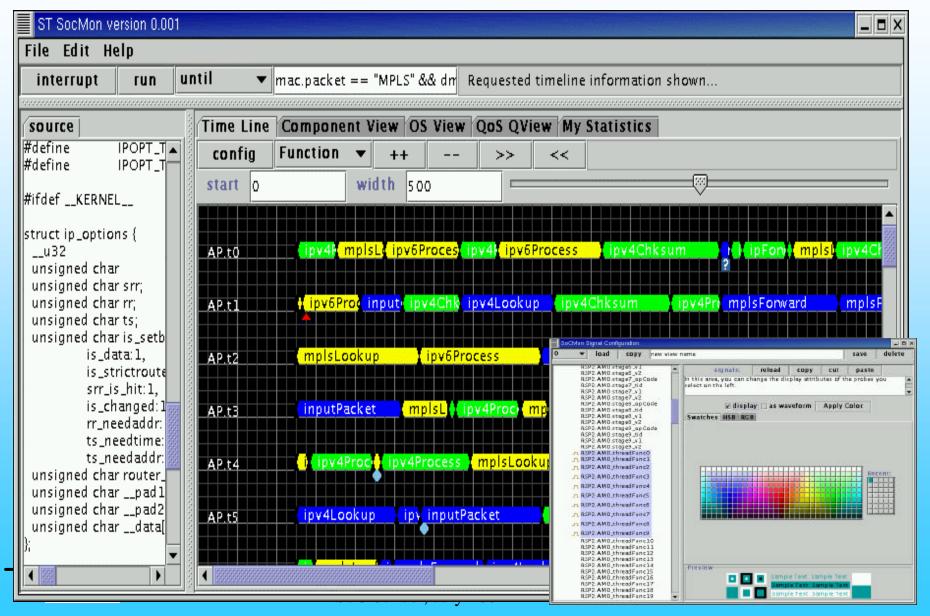

## **SoC-level User-extendable platform**

SoC execution debug

multi-threaded support, backtracking features

SoC execution analysis

Logical, temporal, spatial perspectives

Range of abstraction levels supported

SoC execution control

Well-defined and powerful interface to SoC model

Enables integration with other system software

Interfaces for C++ and scripting languages

#### **SoC Tools – Timeline View**

#### **SoC Tools – Programmer's View**

| ST SocMon version 0.002                 |                                        |                                            |                   | \$newIssue(0, 0)    |             |             |  |  |

|-----------------------------------------|----------------------------------------|--------------------------------------------|-------------------|---------------------|-------------|-------------|--|--|

| File Edit                               | Help                                   | ψΠ                                         | φπεψισσαε(0, 0)   |                     |             |             |  |  |

| interrupt                               | interrupt run until v \$newlssue(0, 0) |                                            |                   |                     |             |             |  |  |

|                                         |                                        |                                            |                   |                     |             |             |  |  |

| source                                  |                                        | Time Line Programmer's Model Pipeline View | Component V       | iew Annotated View  | My Sta      | atistics    |  |  |

|                                         |                                        | Config                                     |                   |                     |             |             |  |  |

| Demo asse                               | embler file I                          |                                            |                   | thread 0 🗗 🖉        |             | thread 1 🗗  |  |  |

| Clicking o                              | n "show source" in                     |                                            |                   |                     |             |             |  |  |

|                                         | er's view will identify the            | thread 0                                   | <b>•</b>          | thread 0 🔻 📥        | <b>v</b> t  | hread 1 🔻 📥 |  |  |

|                                         | e and file that the thread             |                                            | <mark>%0 2</mark> |                     | <b>%</b> 02 |             |  |  |

| is executir                             | ig.                                    | ▼ thread 0 ▼                               | p                 | Show Source         | р           | Show Source |  |  |

|                                         |                                        | add %02, 1, %02                            | rC                | 0                   | rO          | 0           |  |  |

| ".text"<br>.align 4                     |                                        | Single Step Show Source                    | t i               |                     | r1          | e4b3e2f5    |  |  |

| nput:                                   |                                        | 0 01                                       | r2                |                     | r2          | 5a1c4748    |  |  |

| <b>I</b> .                              | ~                                      | r1 00033288                                |                   |                     |             |             |  |  |

| save                                    | %sp,-120,%sp                           | r2 756b96db                                | г3                |                     | r3          | cf84ab9b    |  |  |

| add                                     | %02, 1, %02                            | r3 ead3fb2e                                | r4                |                     | r4          | 44ed0fee 🦉  |  |  |

| sethi                                   | %hi(.LLC0), %o1                        | r4 603c5f81                                | r5                | 9f0624ae            | r5          | ba557441    |  |  |

| or<br>sethi                             | %o1,%lo(.LLC0),%o0<br>%hi(iob),%o1     | r5 d5a4c3d4                                | re                | 5 146e89 <b>0</b> 1 | r6          | 2fbdd894    |  |  |

| or                                      | %o1, %lo(iob), %o2 🦰                   |                                            | r7                | 89d6ed54            | r7          | a5263ce7    |  |  |

| add<br>Id                               | %o2,4,%o1<br>[%o1],%o2                 | r6 4b0d2827                                | rð                | ff3f51a7            | r 8         | 1a8ea13a    |  |  |

| ldub<br>add                             | [%o2], %o0<br>%o2, 1, %o2              | r7 c0758c7a                                | r9                | 74a7b5fa            | r9          | 8ff7058d    |  |  |

| st                                      | %o2, [%o1]                             | r835ddf0cd                                 | r10               | ea101a4d            | r10         | 055f69e0    |  |  |

| stb                                     | %00, [%fp-17]                          | r9 ab465520                                | r11               | 5f787ea0            | r11         | 7ac7ce33    |  |  |

| sll<br>sra                              | %o0, 24, %o1<br>%o1, 24, %o0           | r10 20aeb973                               | r12               | d4e0e2f3            | r12         | f0303286    |  |  |

| cmp<br>bne                              | %o0, -1<br>.LL5                        | r11 96171dc6                               | r13               | 4a494746            | r13         | 659896d9    |  |  |

| nop                                     |                                        | r12 0b7f8219                               | r14               | bfb1ab99            | r14         | db00fb2c    |  |  |

| b                                       | .LL4                                   |                                            |                   |                     |             |             |  |  |

| пор                                     |                                        |                                            | r15               |                     | r15         | 50695f7f    |  |  |

| ldub<br>sll                             | [%fp-17], %o0<br>%o0, 24, %o1          |                                            | r16               | 6 aa82743f          | r16         | c5d1c3d2    |  |  |

| sra                                     | %01,24,%00                             |                                            | r17               | 1fead892            | r17         | 3b3a2825    |  |  |

| cmp<br>be                               | %o0, 46<br>.LL35                       |                                            | r18               | 95533ce5            | r18         | b0a28c78    |  |  |

| nop                                     |                                        | 🗂 thread 31 📄 thread 3                     | 0                 |                     |             |             |  |  |

| 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 |                                        |                                            |                   |                     |             |             |  |  |

## **SoC Tools - Component View**

- □ Shows layout of model components in 2D format

- Model component structure automatically obtained from SystemC model API

- Component graphical representation augmented with configurable information from:

- >> Model signals, attribute values

- » software variable values

- > user-defined function of these primitive values

- >> user-defined functions driving presentation objects

## **Soc Tools - User Defined Views**

- Develop framework that allows end-user to construct application-specific views

- **Two levels: scripting and Java-level**

- Scripting ("easy" extensions): User can write scripts accessing model state, which drives provided presentation objects

- Java-level (power user): Provide Java SoC Monitor IDE environment and framework classes, Java Beans, etc, for extending the user interface

- Framework classes: for model access, control, and presentation

#### **StepNP<sup>TM</sup>: Putting it all Together**

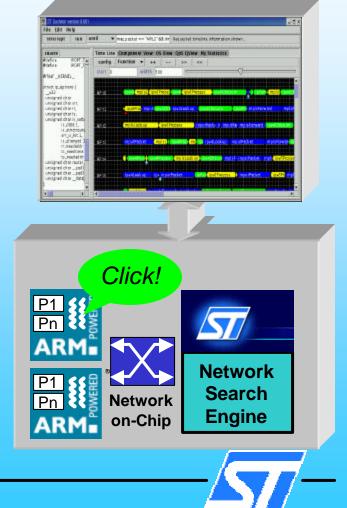

## StepNP<sup>TM</sup> Application: NSE Reference Platform

- Customer learning tool

- Illustrate programming and use of NSE

- Example usage for typical routing applications

- Applications developed using Click Router (NAT, IPv4)

- >> BGP packet traces

- Visualization and control environment

MP SoC School, July 2002

## **StepNP<sup>TM</sup> Benefits**

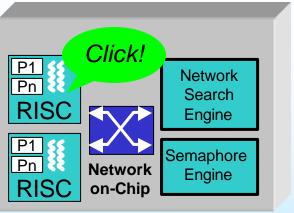

Driver for ST SoC tools/methods Semaphore Pn Network Engine RISC on-Chip Transaction-level modeling > Working on standard instrumentation approach Driver for ST FlexWare eS/W tools >> FlexPerf2 performance analysis > SoC-level debug, FlexCC-based NPU C compiler, ISS tools Reference platform for customers > Including models of ST IP: Network Search Engine, Octagon network-on-chip Environment reused for customer NPUs Vehicle for university interaction

## StepNP<sup>TM</sup> Benefits (2)

- Network Processing training

- > Architecture:

H/W multi-threading, etc.

> Application:

Click router application

- Commercial CAD tool evaluation

- Modelling tools: SystemC, ISS, System-level modeling

Semaphore,

- Verification tools

- **Emerging CAD tool driver:**

- >> Combines two key elements of next gen. SoC's

- 1. Multi-processor

- 2. Network on Chip

## **StepNP<sup>TM</sup> Current Work**

Integration with ST Network Search Engine

Extend SoC debug/analysis tool

SystemC instrumentation methodologies

SOCP transaction-level I/F validation

Integrate with instrumentation methodology

Beta release targeted for Sept. 2002

To selected Univ. and CAD partners

Open Source in 2003

## Next 'Steps'

New Processors, co-processors Tensilica (+ bit-manip. instrns.) Ec. Poly. Montreal LisaTek model integration Univ. Aachen, ST New Interconnect > SPIN LIP6 lab > ST Octagon, AMBA bus Univ. Montreal Application S/W > 4~6 representative applications, ST/Ottawa, LIP6 manually mapped onto threads/processors SoC Tools > Continue development current prototype ST/Ottawa > SystemC instrumentation methods ST/Ottawa

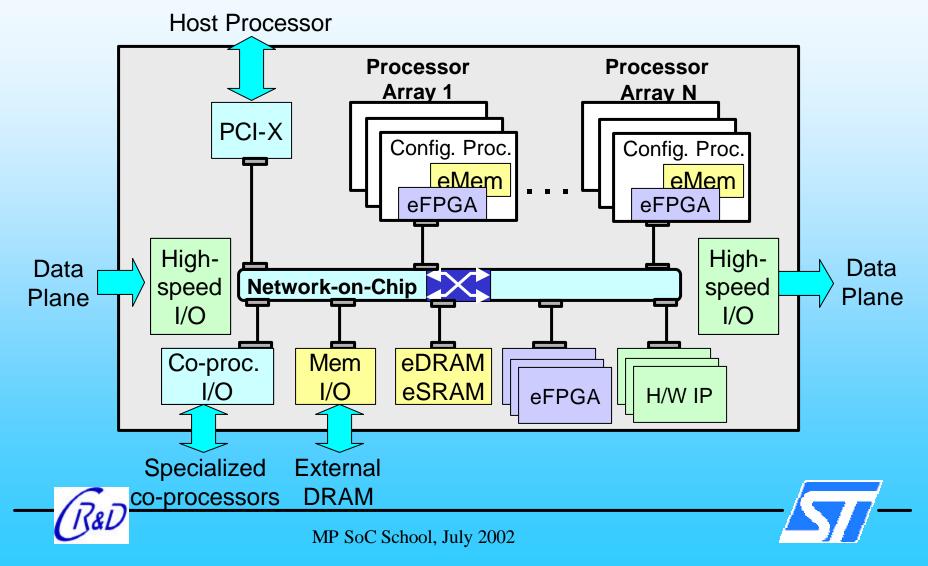

## Outline

Network Processors

StepNP<sup>TM</sup> Research NPU Platform

<u>R&D Needs Outlook</u>

Communication processor architecture of the future?

Key automation technologies

>University interaction

#### **Communication Processor Architecture of the Future?**

## **Key Automation Technologies**

#### **University Research Framework**

## **StepNP<sup>TM</sup> Cooperation**

Academic cooperation

Univ. Montreal and Ecole Polytechnique Montreal

U. Paris LIP6 (SPIN SoC packet-based network)

U. Aachen (ISS/SystemC cosim, eS/W tools)

U. Toronto (Multi-processor compilation)

Polit. Milan (Netw.-on-chip power optimization)

CMC (Canada-wide StepNP distribution)

Others tbd

➤The usual suspects

## Conclusion

NPU's are excellent driver for next generation SoC tools & methods □ StepNP<sup>TM</sup> reference platform > SystemC architecture model framework MIT Click Router application software > SoC methods (SOCP, SIDL) and tool framework ➤Plan for open source in 2003 Many R&D challenges Network-on-Chip architectures Multi-processor compilation