|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Outline                        |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------|

| <ul> <li>Overview, Motivation <ul> <li>Software Related issues in mod</li> </ul> </li> <li>The HdS Concept <ul> <li>A HW-SW Co-Development Prod</li> <li>HdS</li> <li>Isn't HdS Just Software?</li> <li>HdS-API</li> </ul> </li> <li>HdS for Multiprocessor SoCs <ul> <li>MPSoC System</li> <li>HdS Communication System</li> <li>Distributed CORBA Application</li> </ul> </li> <li>HdS Related Standardization Eff <ul> <li>VSIA Overview</li> <li>HdS-DWG Overview</li> <li>DWG Status</li> </ul> </li> </ul> | Management                     |

| MPSoC 2003                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Slide 4 of 74 / Frank Pospiech |

MPSoC 2003

Slide 29 of 74 / Frank Pospiech

|                                                                                                                                    | Outline                         |

|------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|

| <ul> <li>Overview, Motivation</li> </ul>                                                                                           |                                 |

| <ul> <li>The HdS Concept</li> <li>A HW-SW Co-Developmen</li> <li>HdS</li> <li>Isn't HdS Just Software?</li> <li>HdS-API</li> </ul> | t Process                       |

| <ul> <li>HdS for Multiprocessor Sc</li> </ul>                                                                                      |                                 |

| <ul> <li>HdS Related Standardizat</li> </ul>                                                                                       | ion Efforts - VSIA              |

| MPSoC 2003                                                                                                                         | Silde 32 of 74 / Frank Pospiech |

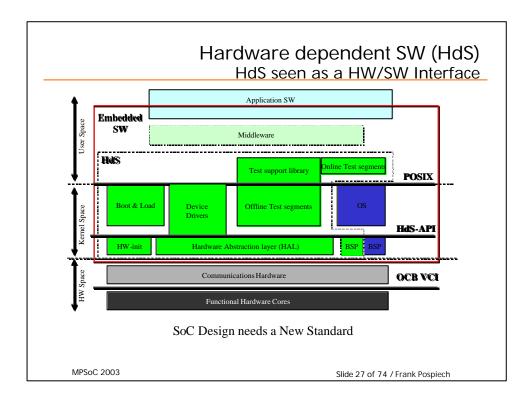

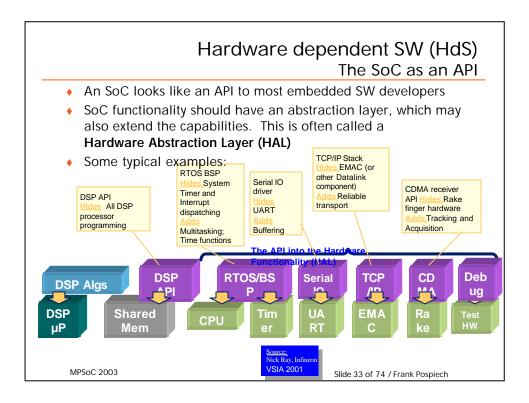

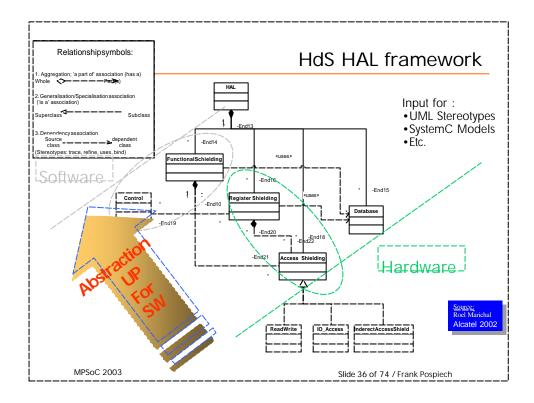

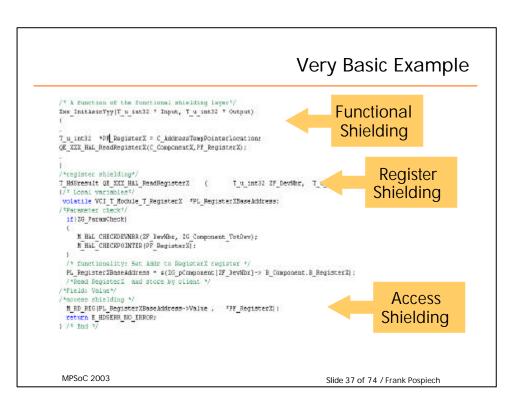

- The Hardware Abstraction layer (HAL) is the ONLY gate towards the HW shielding register access from application providing a SW interface based on:

- structures and/or arrays of basic data types

---> Register Shielding <sup>o</sup> first degree of abstraction.

- Allow SW clients to use the device, without the need of in-depth knowledge of the device.

---> Functional Shielding second degree of abstraction

- ---> Functional Shielding second degree of abstraction

Access shielding:

- a list of macross shielding off the actual access of the memory location to allow the use of the HAL in simulations.

- shielding off the indirect access when applicable.

- Independent of HW base addresses, and number of devices on a board.

MPSoC 2003

Slide 35 of 74 / Frank Pospiech

|                                                                                                                                                                                                                                                         | Outline                         |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|

| <ul> <li>Overview, Motivation</li> <li>The HdS Concept</li> <li>HdS for Multiprocessor         <ul> <li>MPSoC System</li> <li>HdS Communication System</li> <li>Distributed CORBA Applicatio</li> </ul> </li> <li>HdS Related Standardizatio</li> </ul> | n Management                    |

| MPSoC 2003                                                                                                                                                                                                                                              | Slide 40 of 74 / Frank Pospiech |

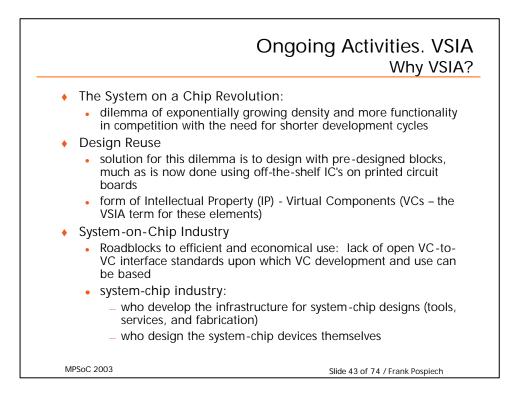

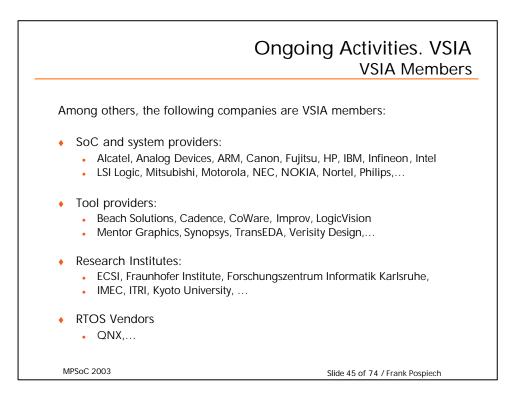

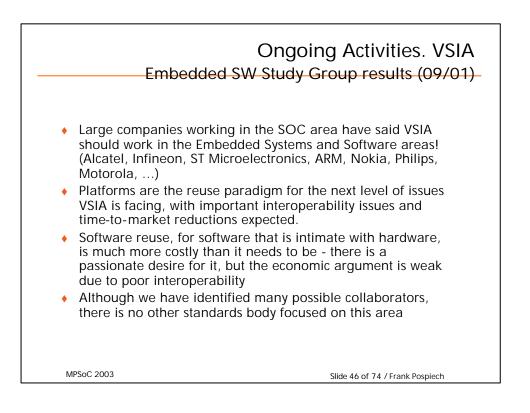

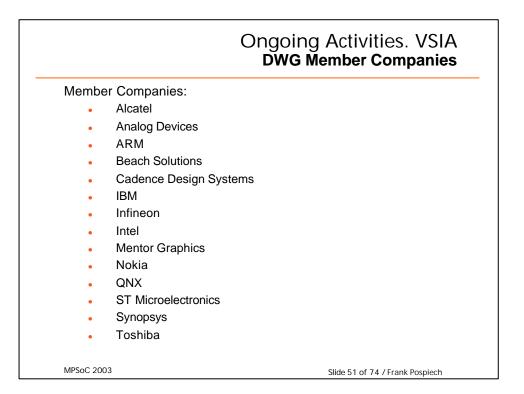

|     | Ongoing Activities. V<br>Who is VS                                                                                                                                                                                                                             |  |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| • ' | Virtual Socket Interface Alliance (VSIA)                                                                                                                                                                                                                       |  |

|     | • formed in September 1996                                                                                                                                                                                                                                     |  |

|     | <ul> <li>goal of establishing a unifying vision for the system-chip industriand the technical standards required to enable the most critical component of the vision: the mix and match of Virtual Components (IP) from multiple sources.</li> </ul>           |  |

| • ' | VSIA Vision:                                                                                                                                                                                                                                                   |  |

|     | <ul> <li>dramatically accelerate system chip development by specifying<br/>open standards</li> </ul>                                                                                                                                                           |  |

| • ' | VSIA Standards Philosophy:                                                                                                                                                                                                                                     |  |

|     | <ul> <li>"open" interface standards, which will allow Virtual Component<br/>to fit quickly into "Virtual Sockets", at both the functional level<br/>(e.g., interface protocols) and the physical level (e.g., clock, test<br/>and power structures)</li> </ul> |  |

|     | <ul> <li>VSIA specifies existing de facto, or open, or proprietary<br/>(reasonable fee and non-discriminatory terms) data formats</li> </ul>                                                                                                                   |  |

|     | <ul> <li>VSIA does not: product development, price or business strategy decisions for individual members</li> </ul>                                                                                                                                            |  |

| MPS | SoC 2003 Slide 44 of 74 / Frank Pospiech                                                                                                                                                                                                                       |  |

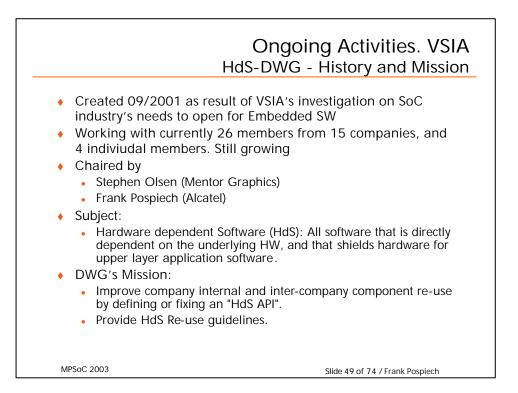

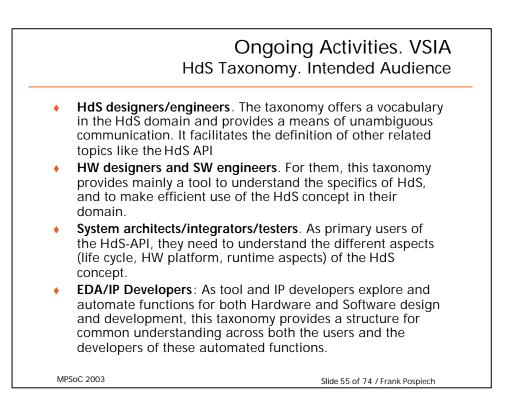

|                                                                                                                                         | Ongoing Activities. VSIA<br>HdS-DWG Charter                                                                                                                                                                                                                                                                 |

|-----------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

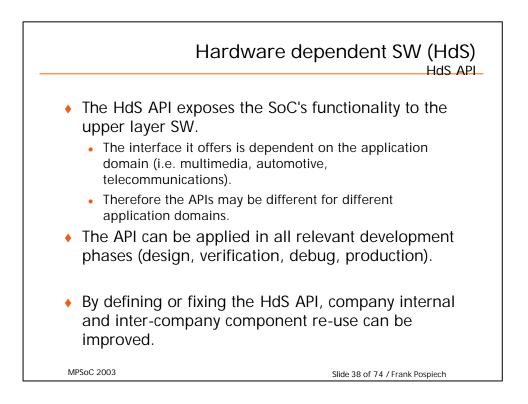

| software layer that interative SoC's HW platform.<br>upper layer SW. HdS cat<br>platform, or SoC design                                 |                                                                                                                                                                                                                                                                                                             |

| component re-use by de<br>exposes the SoC's func<br>interface it offers is dep<br>multimedia, automotive,<br>may be different for diffe | rove company internal and inter-company<br>efining or fixing a "HdS API". The HdS API<br>tionality to the upper layer SW. The<br>endent on the application domain (i.e.<br>telecommunications), therefore the APIs<br>erent application domains. The API can be<br>evelopment phases (design, verification, |

|                                                                                                                                         | clarifies the subject, as well as its different<br>e (HW layer, communication layer,<br>e HdS API).                                                                                                                                                                                                         |

| The DWG addresses SoC-IP providers, and OS provi                                                                                        | providers, system integrators, EDA<br>ders.                                                                                                                                                                                                                                                                 |

| MPSoC 2003                                                                                                                              | Slide 50 of 74 / Frank Pospiech                                                                                                                                                                                                                                                                             |

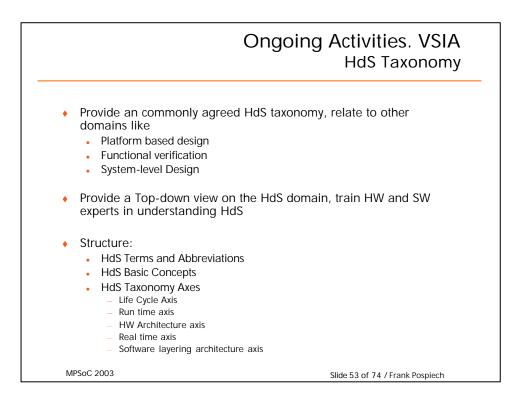

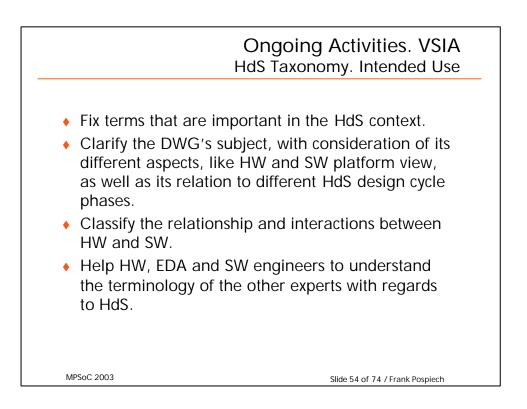

| Hd                                                                                                                                                                                                                  | Ongoing Activities. VSIA<br>S-DWG - Current Main activities                                                                                                |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <ul> <li>be agreed upon in the</li> <li>Definition of HdS specisypace, driver, access sh</li> <li>Relate HdS concepts to platform, SW platform,</li> <li>Determine HdS' archite application software lag</li> </ul> | fic terms (HdS, HdS-API, kernel space, user<br>nielding,)<br>different aspects, like life cycle, HW<br>Real-time<br>ectural relation to HW, middleware and |

| HdS-API:                                                                                                                                                                                                            |                                                                                                                                                            |

| how to provide SoC IP's<br>Define HdS-APIs for dif                                                                                                                                                                  | cs of a common API, that defines the way<br>s functionality to upper layer Software.<br>ferent application domains<br>utomotive, multimedia,)              |

| <ul> <li>Define the HdS-API for<br/>architectures.</li> </ul>                                                                                                                                                       | single-processor and for multi-processor                                                                                                                   |

| MPSoC 2003                                                                                                                                                                                                          | Slide 52 of 74 / Frank Pospiech                                                                                                                            |

|                                                                                                                                                                                                           | Ongoing Activities. VSIA<br>-DWG - Objectives for 2003             |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------|

| <ul> <li>Two major efforts are underv</li> <li>Taxonomy</li> <li>Hardware Abstraction layer,</li> </ul>                                                                                                   | -                                                                  |

| <ul> <li>2003 Goals:</li> <li>Release taxonomy:         <ul> <li>Taxonomy is now in VSIA m</li> <li>HdS-API</li> <li>Contents, syntax, generate</li> <li>Example definition, first</li> </ul> </li> </ul> | al architecture: 2002                                              |

| •                                                                                                                                                                                                         | Specification / Rules to follow<br>Single-processor systems, MPSoC |

| MPSoC 2003                                                                                                                                                                                                | Slide 58 of 74 / Frank Pospiech                                    |

|                           | Appendix. Abbreviations (1/2)                |

|---------------------------|----------------------------------------------|

| API                       | Application programming interface            |

| <ul> <li>ASIP</li> </ul>  | Application Specific Integrated Processor    |

| <ul> <li>CORBA</li> </ul> | Common Object Request Broker Architecture    |

| CPU                       | Central Processing Unit                      |

| DAC                       | Design Automation Conference                 |

| <ul> <li>DATE</li> </ul>  | Design Automation and Test Conference Europe |

| <ul> <li>DSP</li> </ul>   | Digital Signal Processor                     |

| DWG                       | Development Working Group (VSIA)             |

| <ul> <li>GPP</li> </ul>   | General-Purpose Processor                    |

| HAL                       | Hardware Abstraction Layer                   |

| <ul> <li>HdS</li> </ul>   | Hardware dependent Software                  |

| ♦ HW                      | Hardware                                     |

| ♦ IP                      | Intellectual Property                        |

|                           |                                              |

| MPSoC 2003                | Slide 63 of 74 / Frank Pospiech              |

|                          | Appendix. Abbreviations (2/2      |  |

|--------------------------|-----------------------------------|--|

| IPC                      | Inter-process Communication       |  |

| MPSoC                    | Multi-processor SoC               |  |

| <ul> <li>OFLT</li> </ul> | Offline Test                      |  |

| OS                       | Operating System                  |  |

| RISC                     | Reduced Instruction Set Computer  |  |

| RPC                      | Remote Procedure Call             |  |

| RTOS                     | Real-time Operating System        |  |

| SoC                      | System on Chip                    |  |

| SUD                      | System under Design               |  |

| SW                       | Software                          |  |

| VC                       | Virtual Component                 |  |

| VSIA                     | Virtual Socket Interface Alliance |  |