## Five Ways to Design Future SoC

Kazuaki J. Murakami Director Computing & Communications Center Kyushu University E-mail: murakami@cc.kyushu-u.ac.jp

Kazuaki Murakami©2000-2004

## Messages in This Talk

- Platform-based design will dominate the future SoC designs

- Among many platform architectures, "multiple reconfigurable processor" seems promising to me

- Anyway, we need a comprehensive quantitative analysis on the cost<sup>3</sup>/performance of these architectures

- This talk will give just some taxonomies and a qualitative comparison among them

Cost<sup>3</sup>=Design Cost  $\times$  Production Cost  $\times$  Running Cost

## SoC Design... What Are the Essentials?

- How do we design and implement custom logic?

- Custom logic is a logic, or function (e.g., MPEG4's ME/MC), which cannot or shall not be implemented on general-purpose processor (e.g., ARM) for some performance or power reason.

- There are at least five ways to implement such custom logic...

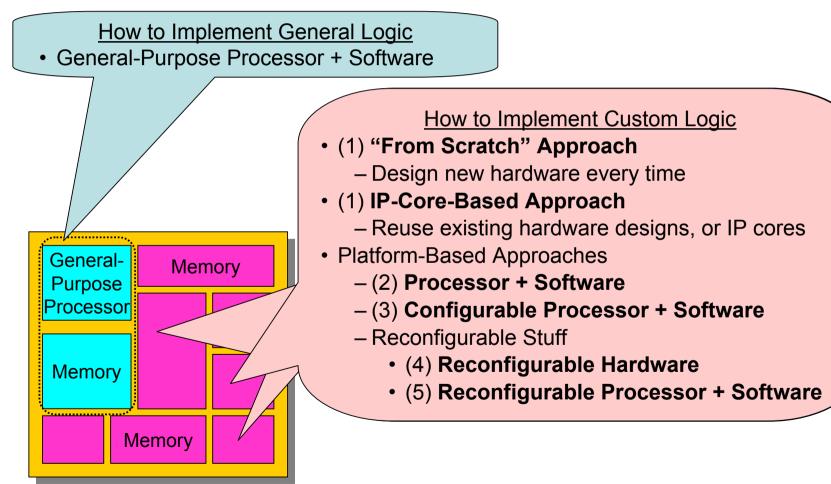

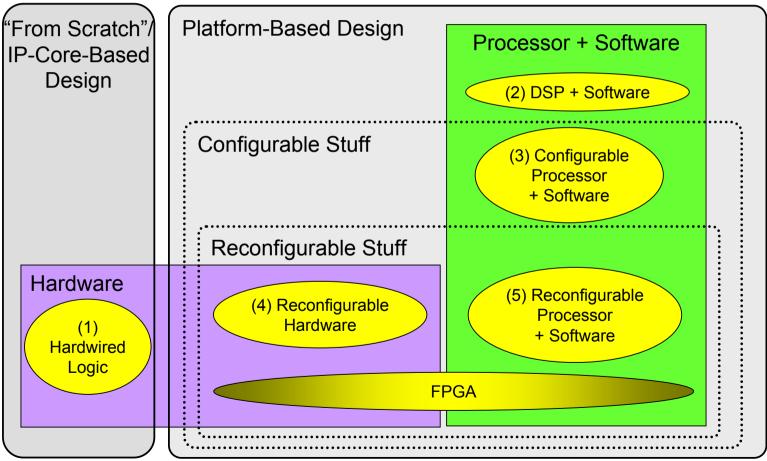

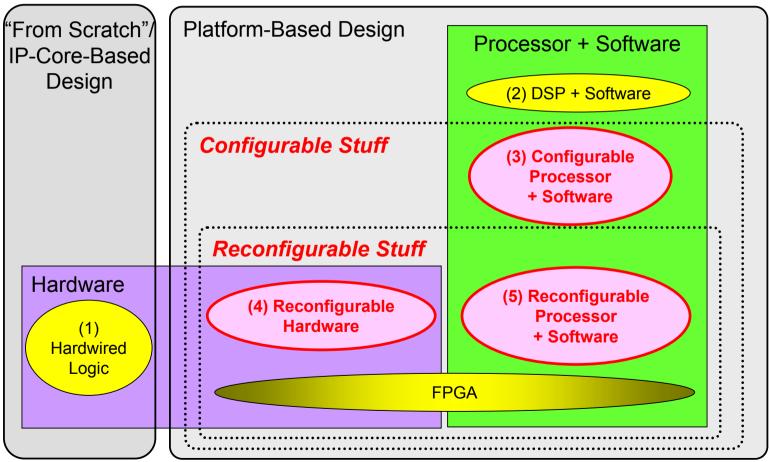

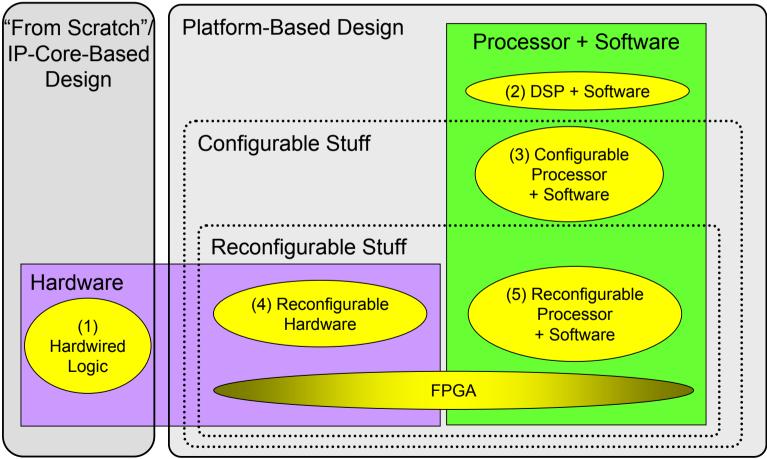

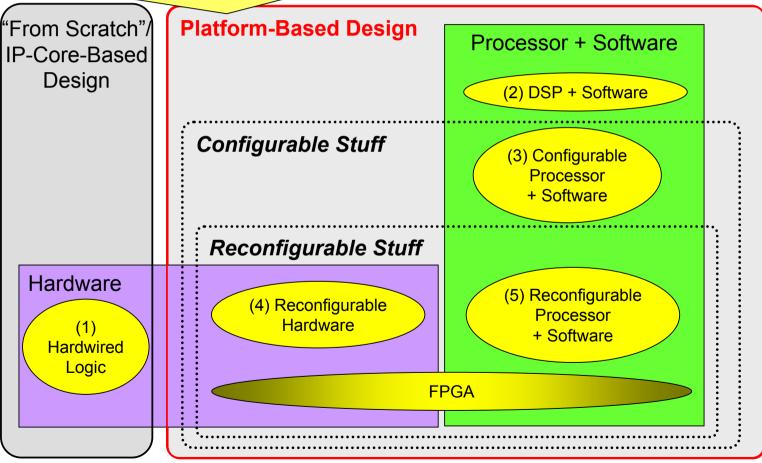

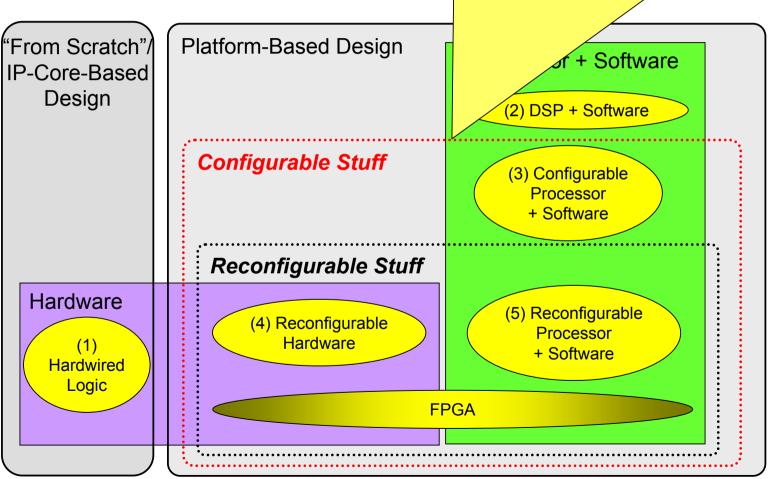

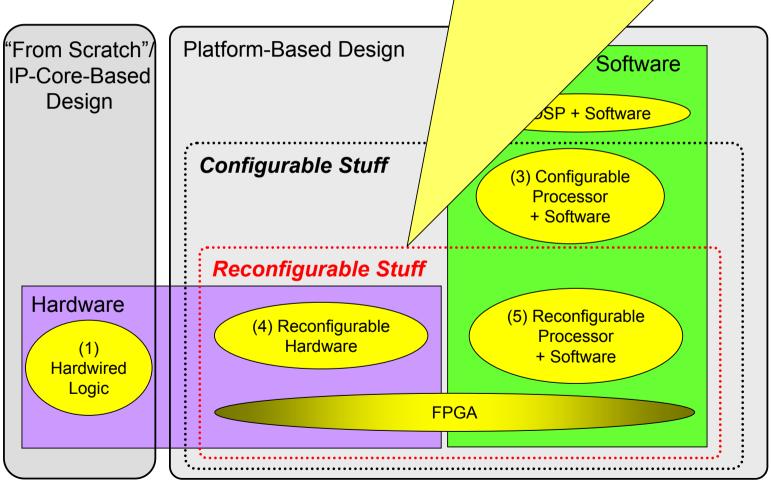

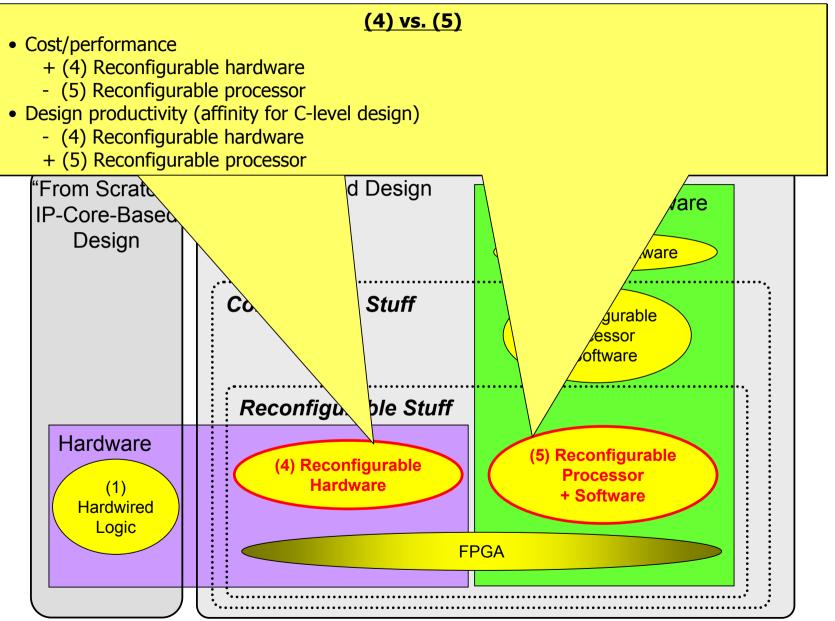

## Five Ways to Design & Implement Custom Logic

## Five Ways to Design & Implement Custom Logic

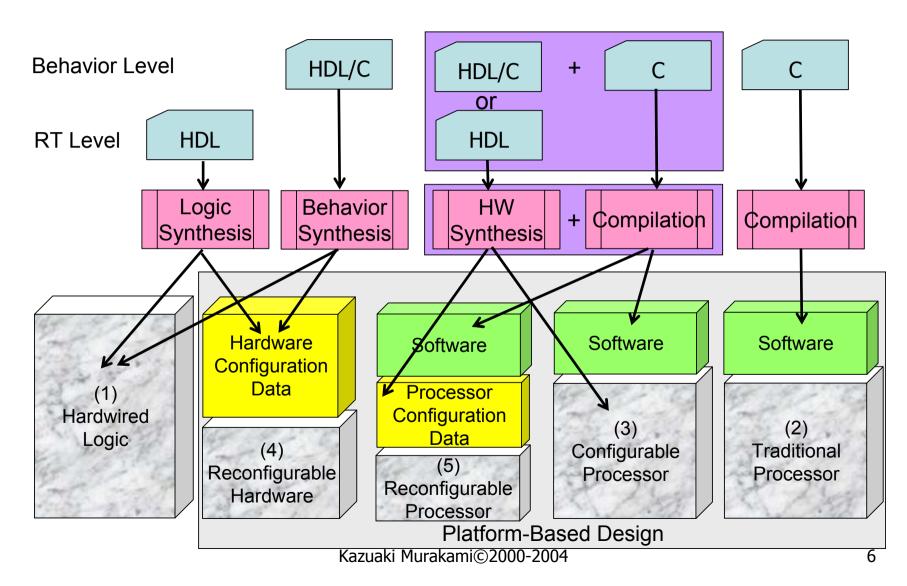

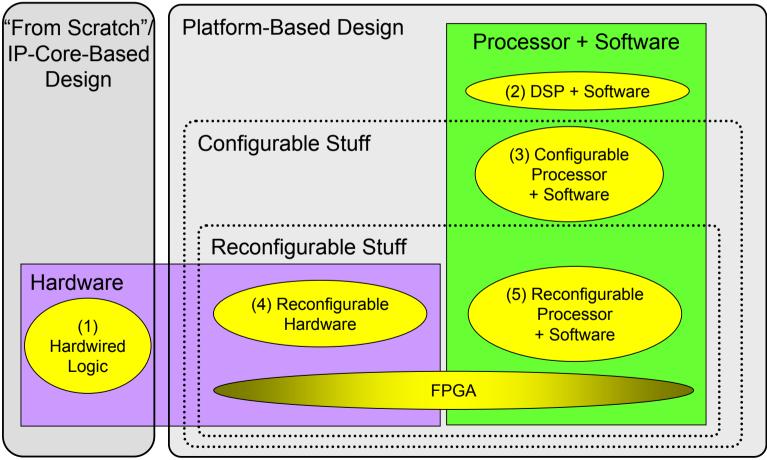

## Five SoC Design Flows

## What Is Platform?

- Platform is a kind of "common" facilities used for implementing a variety of custom logic independently of the characteristics of the custom logic.

- Analogy: Chasses for automobiles

- Platform-based SoC design: SoC design methodologies by means of the platforms

- Counterparts: "From scratch" design, IP-core-based design

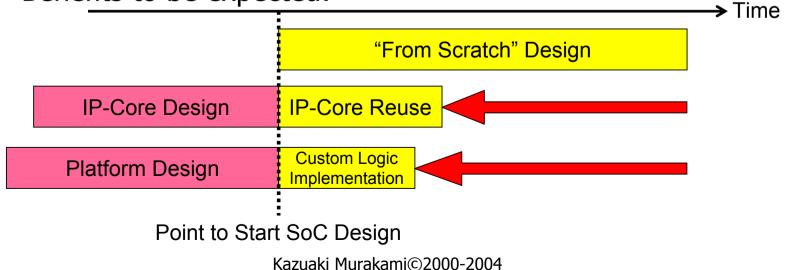

- Benefits to be expected:

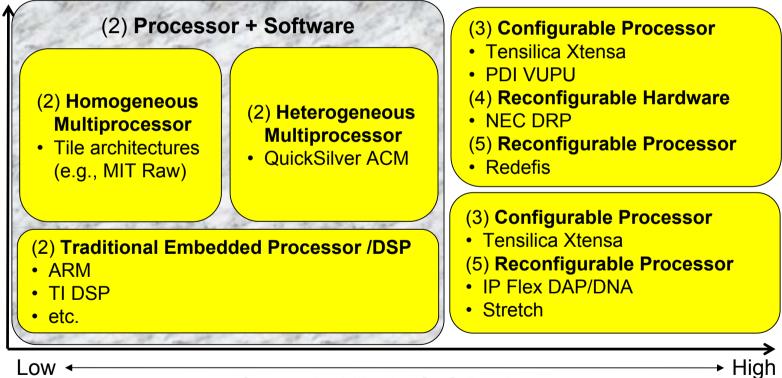

## Design Space of Platform Architectures

Multiprocessor-

Oriented

Customizability by SoC Designers

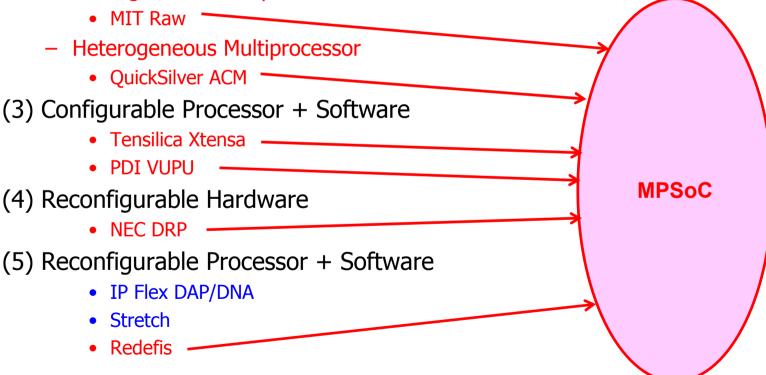

## List of Platform Architectures

- (2) Processor + Software

- Traditional Embedded Processor or DSP

- Homogeneous Multiprocessor

## Five Ways to Design & Implement Custom Logic

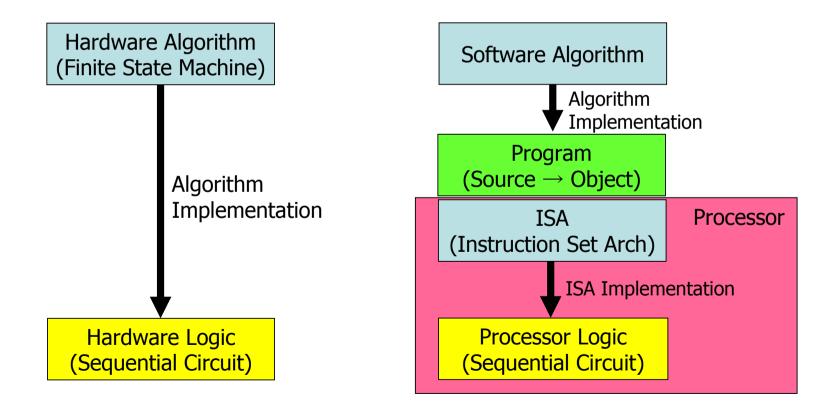

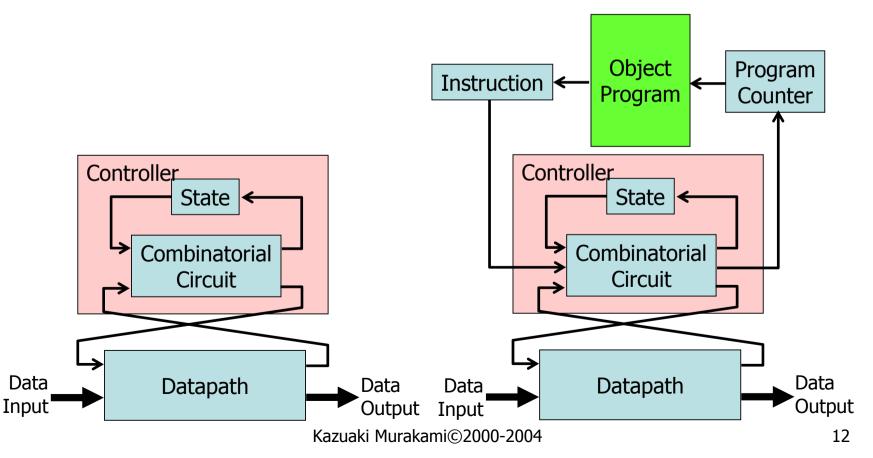

## Hardware vs. Processor + Software

• Hardware

• Processor + Software

### Hardware vs. Processor + Software

• Hardware

• Processor + Software

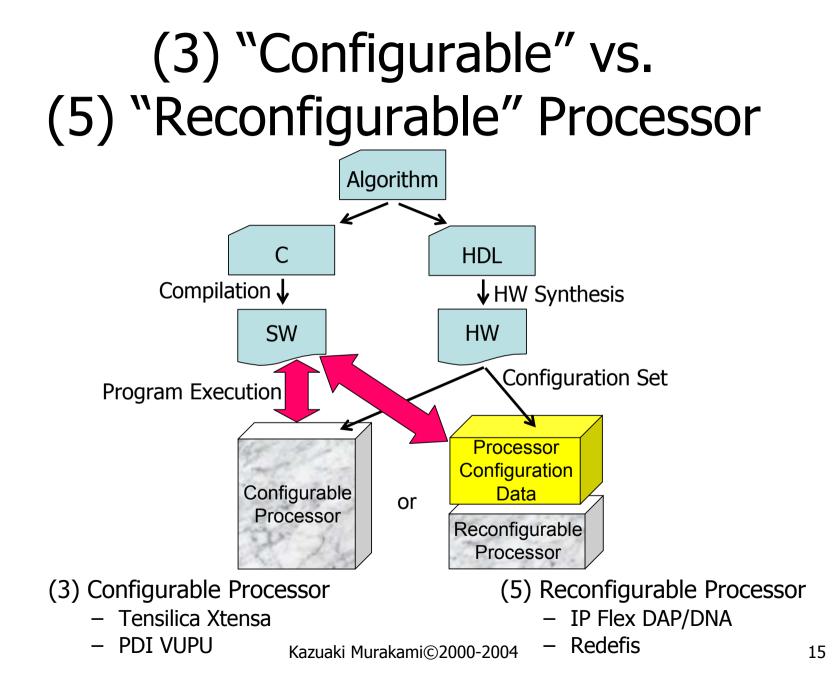

## The Ways (3) – (5) to Design & Implement Custom Logic

## What Are "Configurable" and "Reconfigurable"?

- Some functions to be implemented in hardware or processor can be designed and set by SoC designers

- Configurable: Can be set just once

- *Reconfigurable*: Can be set multiple times

|                  | Hardware                       | Processor                       |  |

|------------------|--------------------------------|---------------------------------|--|

| Non-configurable |                                | Traditional Processor           |  |

| Configurable     | Traditional Hardware<br>Design | (3) Configurable<br>Processor   |  |

| Reconfigurable   | (4) Reconfigurable<br>Hardware | (5) Reconfigurable<br>Processor |  |

## A Taxonomy

- w.r.t. HW vs. SW, Configurability, and Reconfigurability -

| When is a HW/processor configuration generated? |                                        |                                |                                                                                                       |                                                                                                               |

|-------------------------------------------------|----------------------------------------|--------------------------------|-------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------|

|                                                 | How many can the configuration be set? |                                | Hardware                                                                                              | Processor + Software                                                                                          |

|                                                 |                                        | When is the configuration set? |                                                                                                       |                                                                                                               |

| -<br>(Non-<br>configurable)                     | -                                      | -                              | -                                                                                                     | •(3) Traditional Processor/DSP<br>•(3) Multiprocessor<br>–QuickSilver ACM                                     |

| Static<br>generation                            | Once                                   | -                              | •(1) Hardwired Logic                                                                                  | •(3) Configurable Processor<br>–Tensilica Xtensa<br>–PDI VUPU                                                 |

|                                                 | Multiple<br>times                      | Offline reconfiguration        | •Traditional FPGA                                                                                     | •Traditional FPGA                                                                                             |

|                                                 |                                        | Online<br>reconfiguration      | <ul> <li>Dynamic Reconfigurable<br/>FPGA</li> <li>(4) Reconfigurable Hardware<br/>–NEC DRP</li> </ul> | •Dynamic Reconfigurable FPGA     •(5) Reconfigurable Processor     –IP Flex DAP/DNA     –Stretch     –Redefis |

| Dynamic<br>generation                           | Multiple<br>times                      | Online<br>reconfiguration      | •?                                                                                                    | •?                                                                                                            |

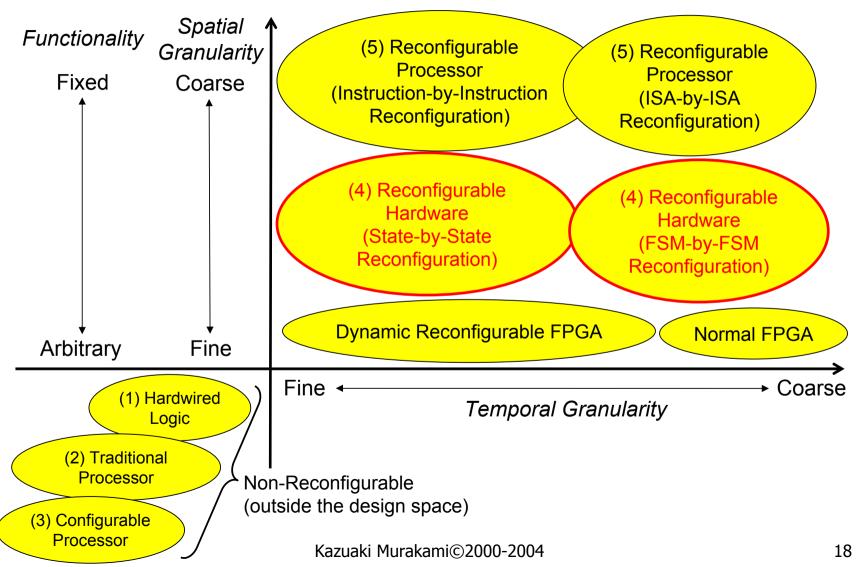

## Design Space on Reconfigurability

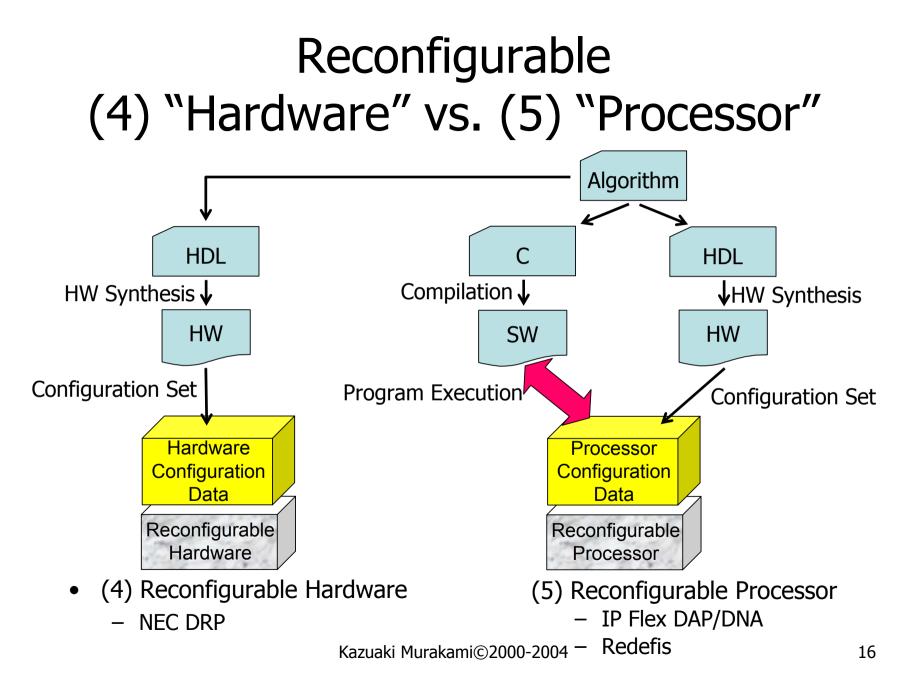

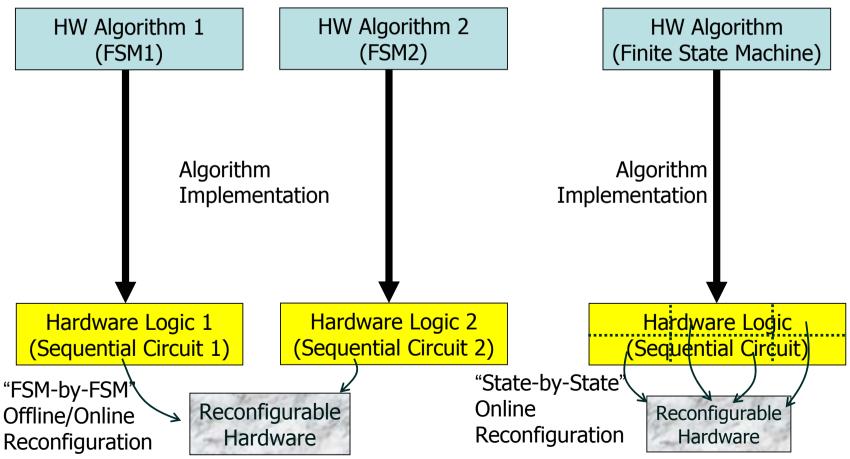

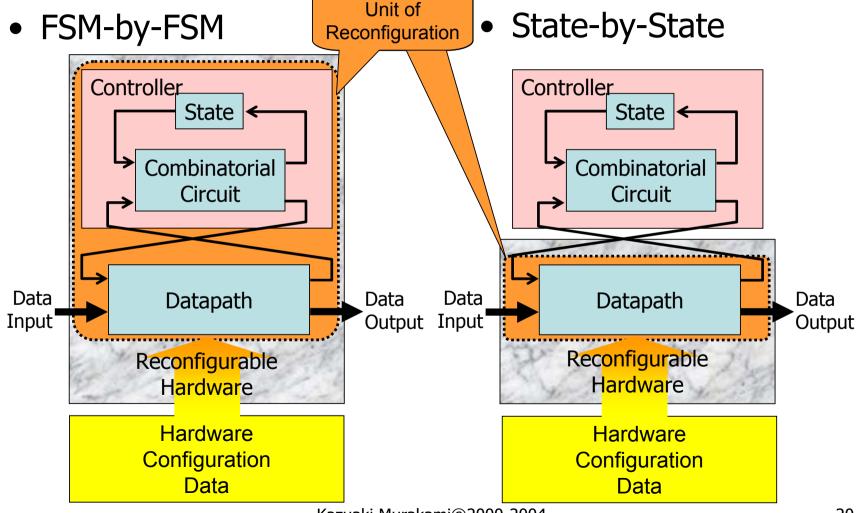

## (4) Reconfigurable HardwareTemporal Granularity -

State-by-State

• FSM-by-FSM

## (4) Reconfigurable HardwareTemporal Granularity -

#### Kazuaki Murakami©2000-2004

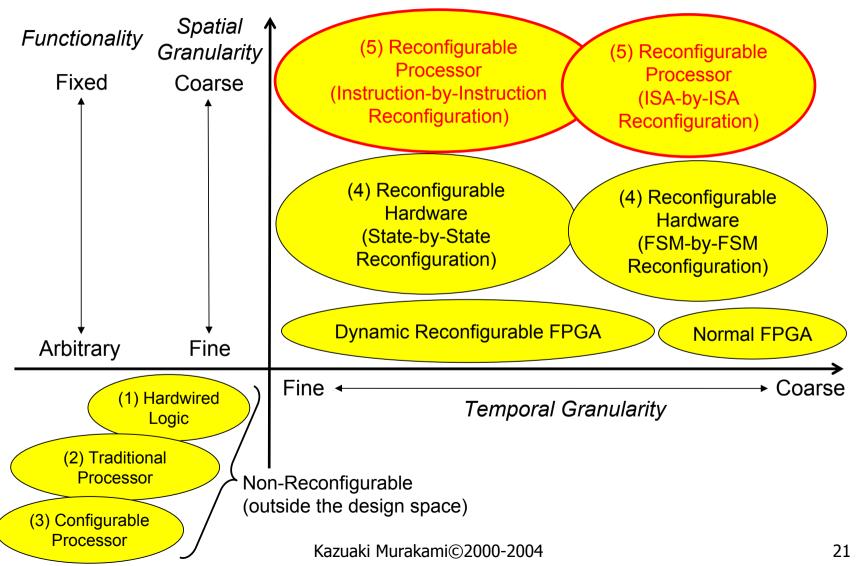

## Design Space on Reconfigurability

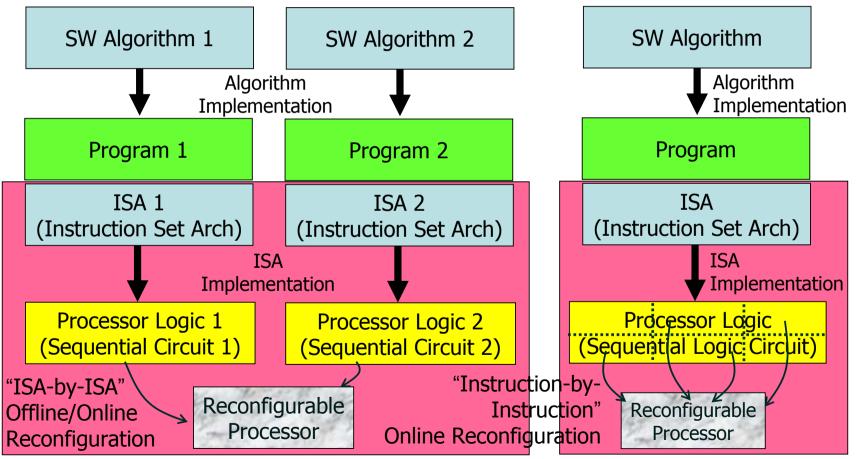

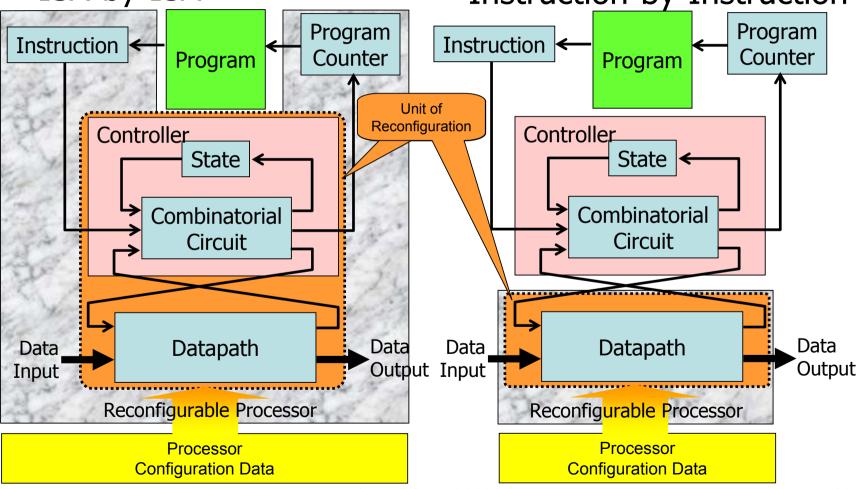

## (5) Reconfigurable Processor- Temporal Granularity -

• ISA-by-ISA

• Instruction-by-Instruction

# (5) Reconfigurable Processor - Temporal Granularity • ISA-by-ISA • Instruction-by-Instruction

Kazuaki Murakami©2000-2004

## Five Ways to Design & Implement Custom Logic

#### (2), (3), (4), and (5)

- Divide SoC design into two tasks: (i) platform design, and (ii) custom logic implementation on the platform

- Spend most of time on the custom logic implementation on the platform, and then reduce the TAT (turn-around time) of SoC

- Reuse a single platform-based SoC design for multiple applications like a "general-purpose" SoC

#### (3), (4), and (5)

- Accommodate the HW/processor configuration to the characteristics of the custom logic to be implemented

- + Improve the cost/performance against (2) "DSP + software" approaches

- May suffer the increase of the TAT of SoC for the accommodation task

#### (4) and (5)

Still accommodate the HW/processor configuration to the characteristics of the custom logic to be implemented even after the SoC is fabricated

- + Reduce the TAT of SoC more than (3) "configurable processor" approaches

- May suffer the increase of area and performance overhead

## Summary

- Platform-based design will dominate the future SoC designs

- Among many platform architectures, "multiple reconfigurable processor" seems promising to me

- Anyway, we need a comprehensive quantitative analysis on the cost<sup>3</sup>/performance of these architectures

- This talk gave just some taxonomies and a qualitative comparison among them

Cost<sup>3</sup>=Design Cost  $\times$  Production Cost  $\times$  Running Cost

### Some References

- (2) Processor + Software

- Traditional Embedded Processor or DSP

- Homogeneous Multiprocessor

- MIT Raw → http://catfish.csail.mit.edu/raw/

- Heterogeneous Multiprocessor

- QuickSilver ACM → http://www.quicksilvertech.com/

- (3) Configurable Processor + Software

- Tensilica Xtensa → http://www.tensilica.com/

- PDI VUPU → http://www.pdi.co.jp/

- (4) Reconfigurable Hardware

- NEC DRP

- (5) Reconfigurable Processor + Software

- IP Flex DAP/DNA → http://www.ipflex.com/

- Stretch → http://www.stretchinc.com/

- Redefis

### **Backup Slides**

### Redefis (<u>Redefinable ISA Processor</u>): A Reconfigurable Processor

Normal Reconfigurable Redefis (Redefinable ISA Processor) Processor Algorithm **ISA Gen** Algorithm ጉ C C HDL ISA ↓Compilation ↓ Compilation ↓ HW Synthesis SW HW SW HW Configuration Program Program Configuration Execution Setting Execution Setting Processor Processor Configuration Configuration Data Data Reconfigurable Reconfigurable Processor Processor