### Power Management in Wireless SOCs

Jan M. Rabaey Scientific Co-Director BWRC Director GSRC EECS Dept. Univ. of California, Berkeley

With contributions of M. Sheets and H. Qin

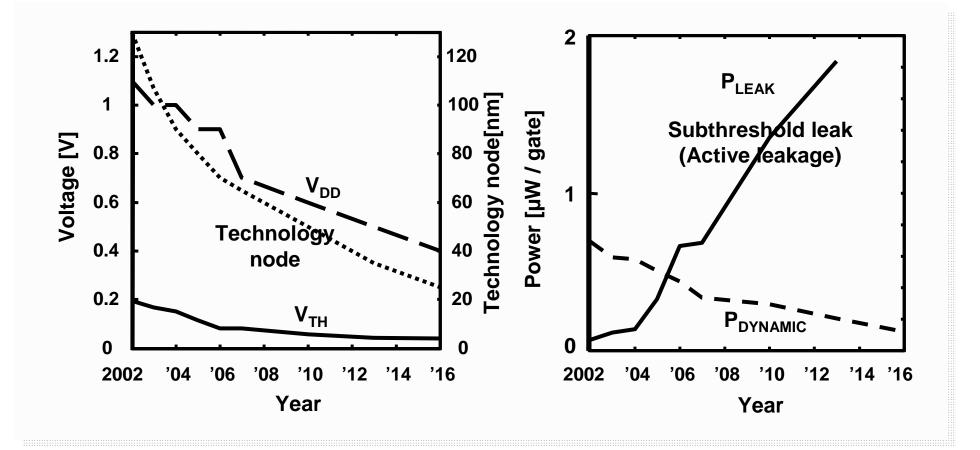

#### The Leakage Challenge (1)

T. Sakurai, ISSCC 03

### The Leakage Challenge (2)

Source: S. Borkar, Intel

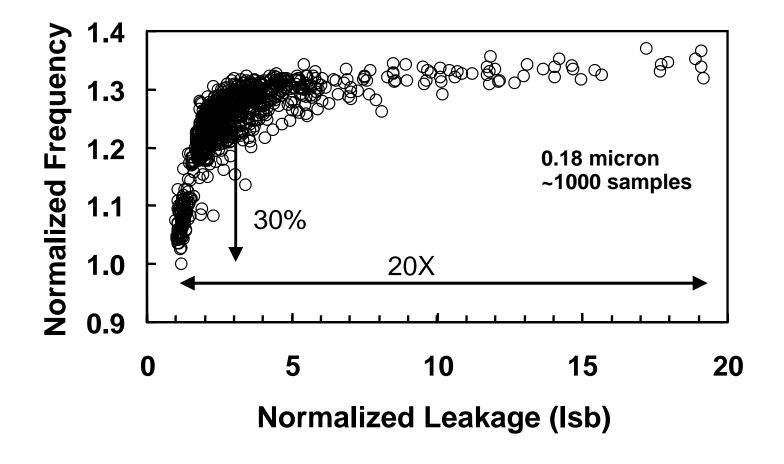

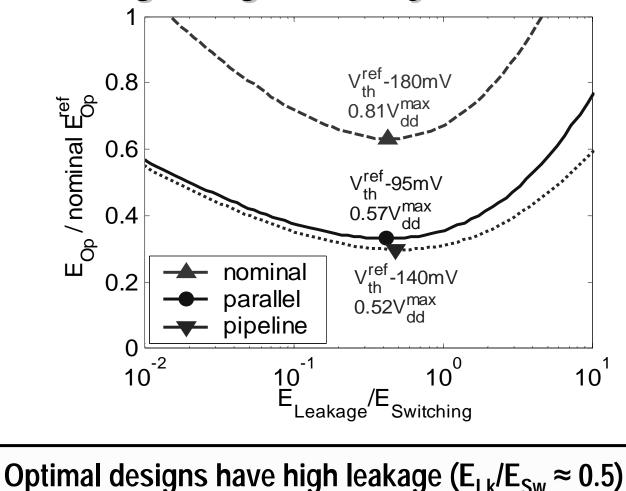

#### The Other Side of the Story: Leakage is good for you!

Must adapt to process variations and activity

Source: P. Gelsinger (DACO4)

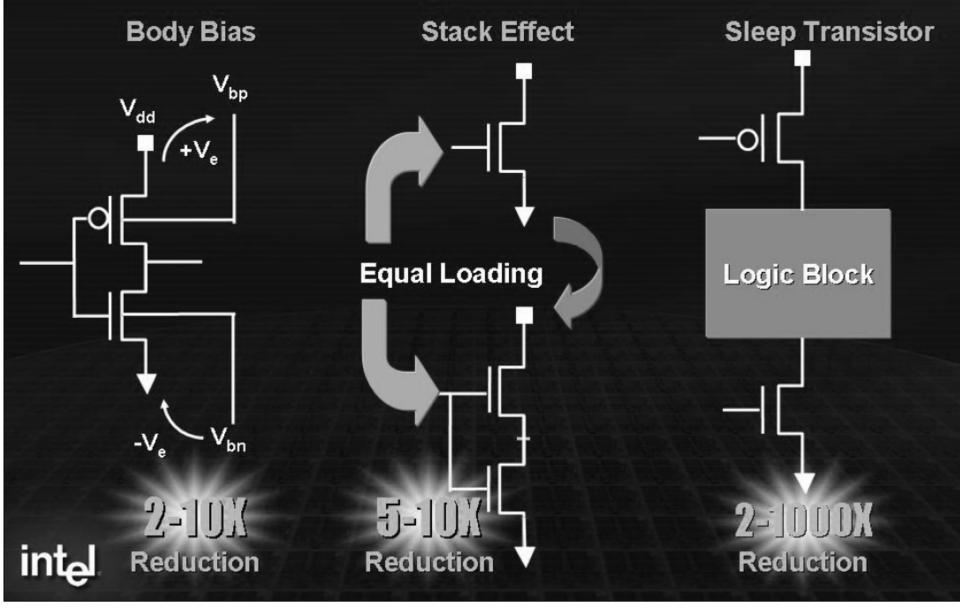

#### Leakage Control

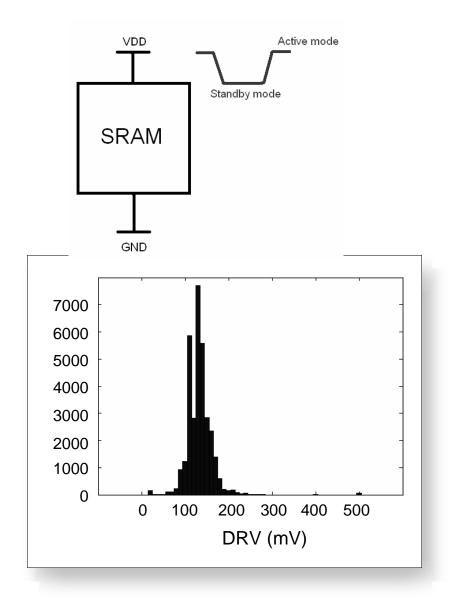

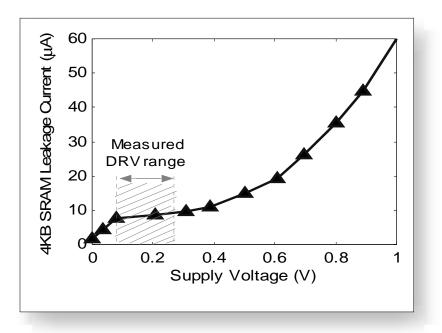

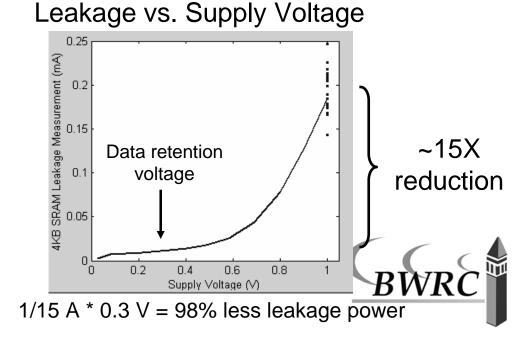

#### What to do about memory? "The data retention voltage (DRV)

Data obtained from 4K bytes SRAM test-chip, implemented in 130 nm CMOS

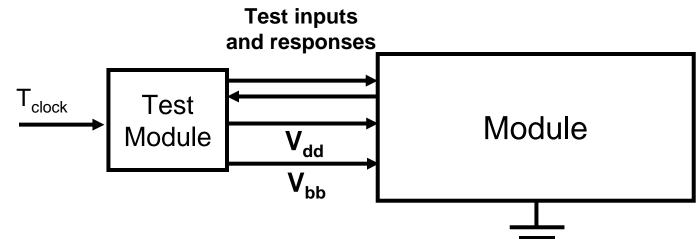

# **Calibrating for Process Variations**

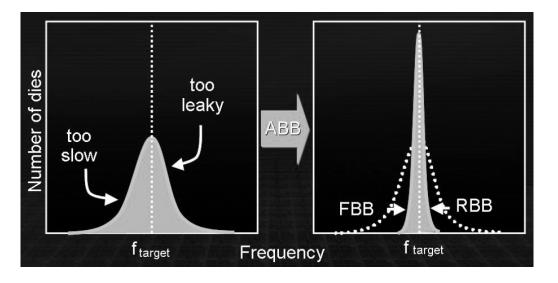

Most variations are systematic, and can be adjusted for at start-up time using one-time calibration!

- Relevant parameters:  $T_{clock}$ ,  $V_{dd}$ ,  $V_{th}$

- Can be easily extended to include leakage-reduction and power-down in standby

- Achieves the maximum power saving under technology limit

- Inherently improves the robustness of design timing

- Minimum design overhead required over traditional design methodology

### Adaptive Body Biasing

Source: P. Gelsinger (DAC04)

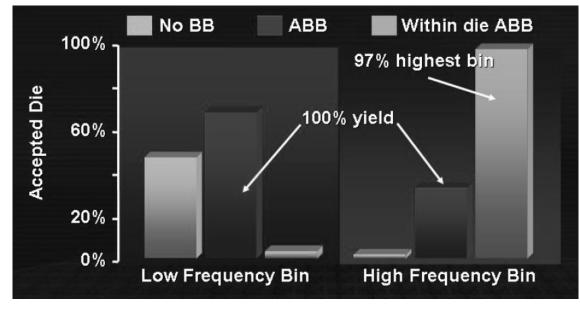

# Introducing "Power Domains (PDs)"

Similar in Concept to "Clock Domains", but extended to include power-down (really!) and local supply and threshold voltage management.

# Introducing "Power Domains (PDs)"

Who is in charge?

#### A Case Study — Protocol Processor for Wireless Sensor Networks

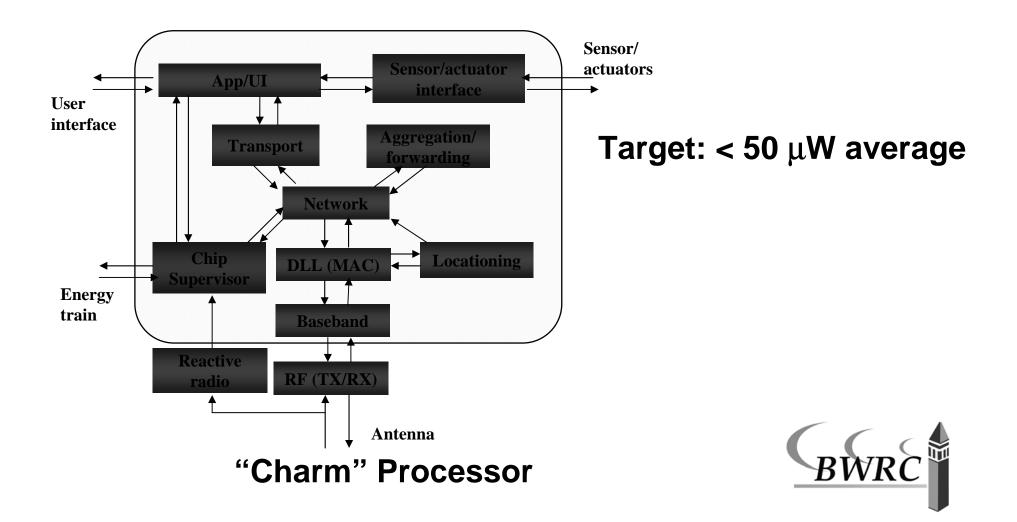

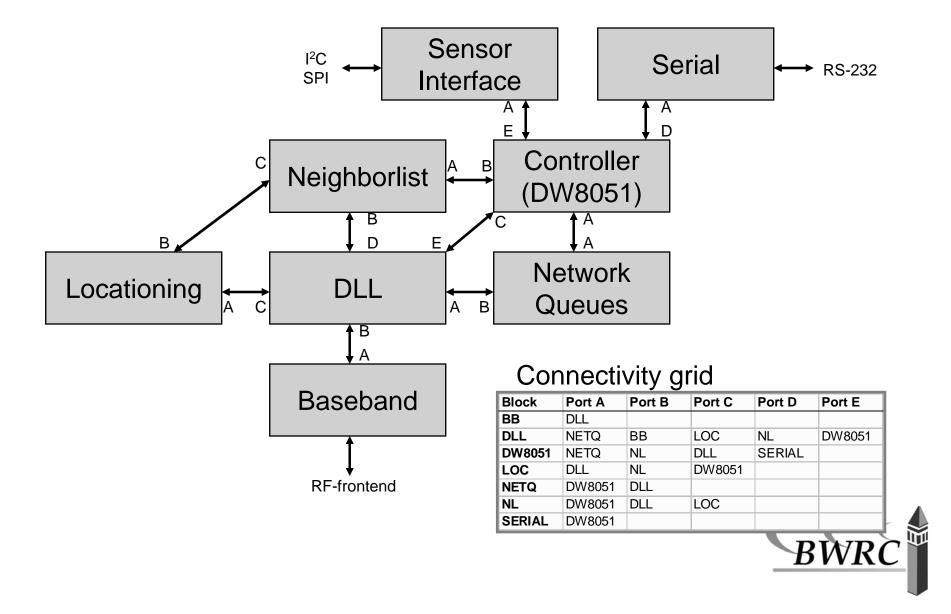

#### Charm Architecture

- 1 V operational supply voltage

- 16 MHz Clock Frequency

- Simple processor aided with dedicated accelerators

- Reactive inter- and intra-chip signaling

- Aggressive Use of Power-Domains

- Chip Supervisor Manages Activity

#### Call a Plumber... This Thing Leaks!

|              |            | Est. leakage | e @1V (uW) |   |

|--------------|------------|--------------|------------|---|

| Block        | Area (um²) | Logic        | Memory     |   |

| Locationing  | 337990     | 39.9         |            |   |

| DW8051       | 63235      | 8.2          | 2880.0     | - |

| Interface    | 6098       | 0.8          |            |   |

| Neighborlist | 21282      | 2.5          | 13.5       |   |

| Serial       | 2554       | 0.4          |            |   |

| NetQ         | 6296       | 0.7          | 108.0      |   |

| DLL          | 126846     | 17.4         | 13.5       |   |

| Supervisor   | 51094      | 6.4          |            |   |

|              |            |              |            |   |

| Total        |            | 76.3         | 3015.0     | • |

64KB SRAM for SW code and data

— 30X the target power...just in leakage!!

# Hey buddy, turn down the voltage!

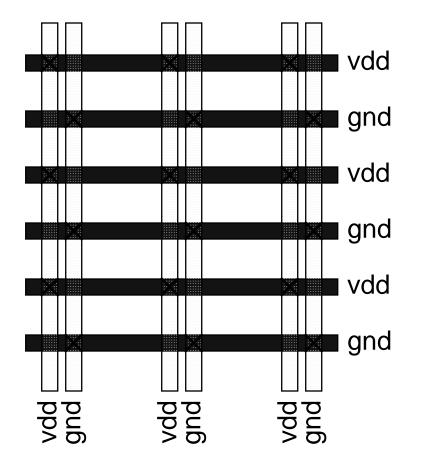

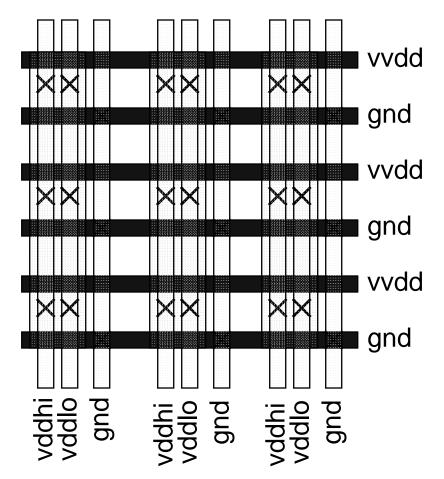

#### Gated Power Architecture

- Vddhi active mode voltage (nominal)

- Vddlo standby mode voltage allows retention of state

- Switch design can be independent of block size

- Built in buffer distributes driver circuitry

- Enables creation of a buffer tree during STBY signal routing

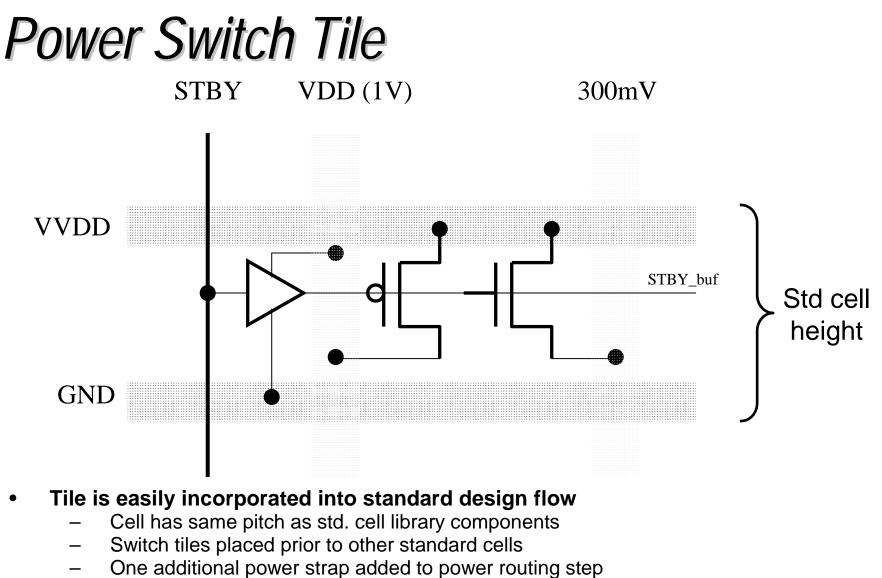

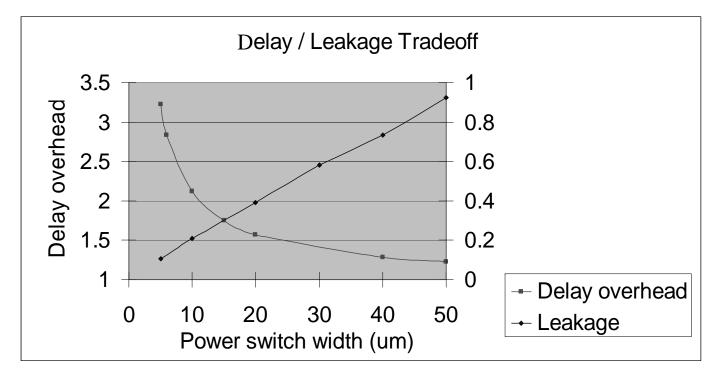

#### Power Switch Sizing

- Switch sizing enables trade-off between delay overhead and leakage

- Delay scale normalized to un-gated design

- Leakage scale normalized to case when switch size is 50  $\mu$ m

- Timing slack determines delay requirement

- Control domains (DLL, processor) tolerant of delay overhead

- Datapath domains (locationing) longer critical paths, less tolerant of delay overhead

H. Qin

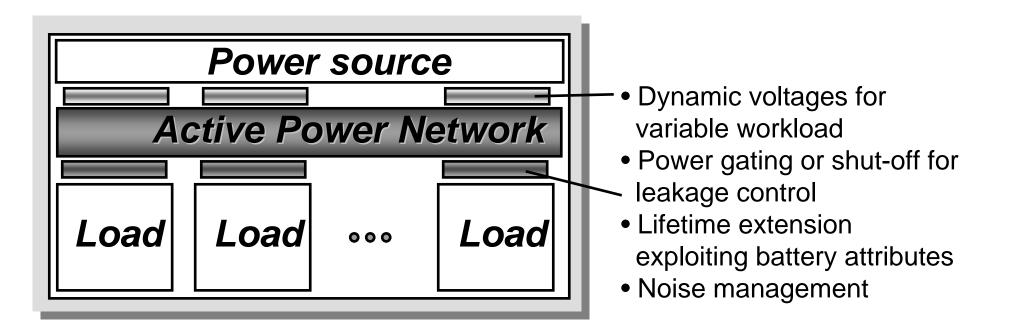

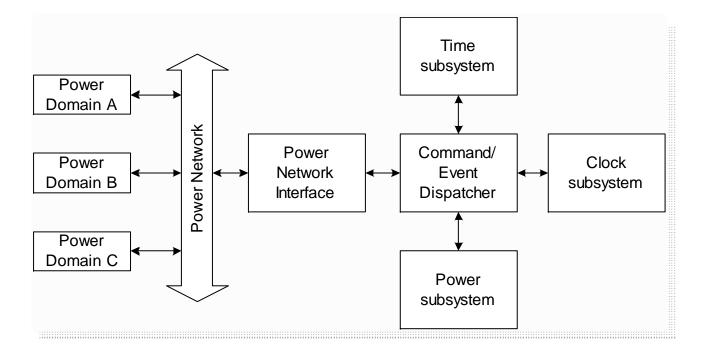

## System Supervisor

- How to control block activation/deactivation?

- System supervisor centralizes power control

- Power subsystem gates block power rails

- Clock subsystem gates block clocks

- Timer subsystem system time-wheel and wake-up timers

### Power Subsystem

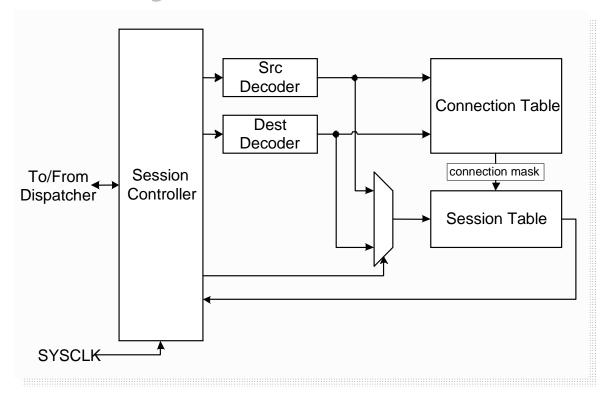

- Session controller opens/closes sessions

- Connection table holds connectivity masks and performs port address translation

- Session table keeps track of open sessions

#### Charms Sub-blocks and Connectivity

#### **Power Session Table**

Before a power domain can communication with a neighbor, it must first open a session

#### **Power policy:**

#### A power domain can sleep if...

- 1) It has closed all its sessions

- 2) No other domain has a session open with it

- 3) It wants to go to sleep

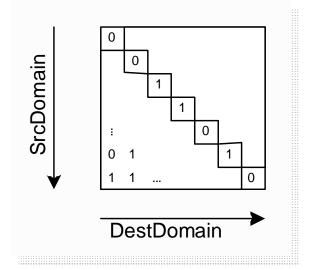

#### Session Table

A '1' in row i means that power domain i has an open a session with another domain

A '1' in column k means that another domain opened a session with domain k

A '1' in entry (i, i) is domain i's self-sleep bit

can\_sleep(i) = reduction\_nor(row i) and reduction\_nor(col i)

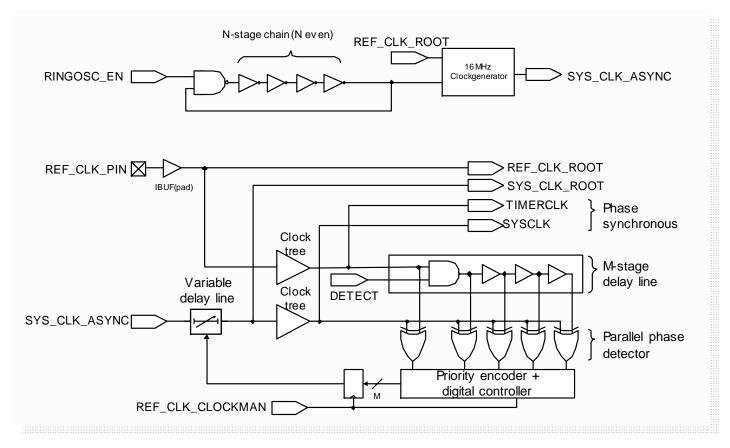

# **Clocking Subsystem**

- Low frequency external clock (32 KHz)

- Generated, switchable, higher frequency clock (16 MHz)

- Two clocks are made phase-synchronous using DLL

- Control signals are generated by system supervisor

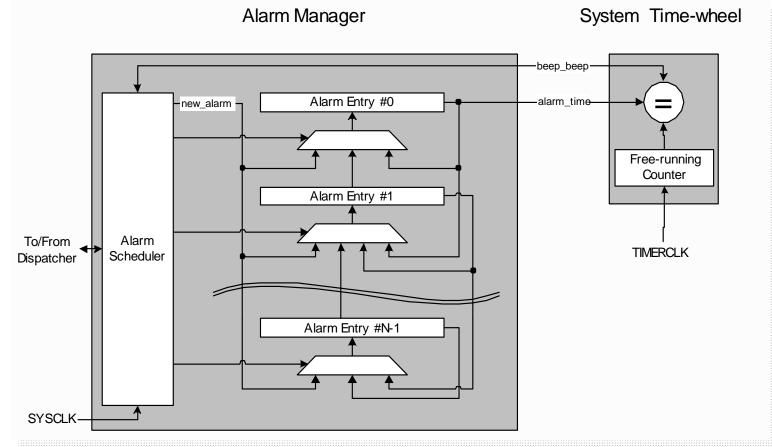

### Timer Subsystem

- Centralized system time-wheel

- Blocks schedule wake-up alarms

- Eliminates other large counters so blocks can sleep

- Allows power domains to sleep

- Very low switching activity factor

- SYSCLK is disabled during deep sleep

- Serial (ripple) comparison starting with MSB

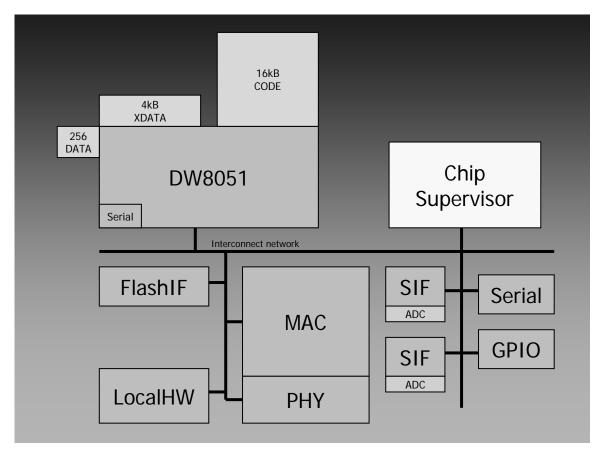

#### Wireless Sensor Network Protocol Processor

|                       | а. |        | Base<br>Band      | Voltage<br>Conv     |  |

|-----------------------|----|--------|-------------------|---------------------|--|

| 64                    | к  |        | GPIO<br>Interface | Serial<br>Interface |  |

| memory                |    |        | DW8051<br>µc      |                     |  |

| - Ne                  |    | System | Netv              | vork                |  |

| Locationing<br>Engine |    |        |                   | Queues              |  |

| Technology              | 0.13μ CMOS                            |  |  |

|-------------------------|---------------------------------------|--|--|

| Chip Size               | 3mm x 2.75mm =<br>8.2 mm <sup>2</sup> |  |  |

| Transistor Count        | 3.2M                                  |  |  |

| Gate Count              | 62.5K gates                           |  |  |

| Clocks Freqs            | 16MHz(Main),<br>1MHz(BB)              |  |  |

| On Chip memory          | 68Kbytes                              |  |  |

| Core Supply<br>Voltages | 1V(High) –0.3V(Low)                   |  |  |

| On_Power                | < 1 mW                                |  |  |

| Standby Power           | μWs                                   |  |  |

In fab

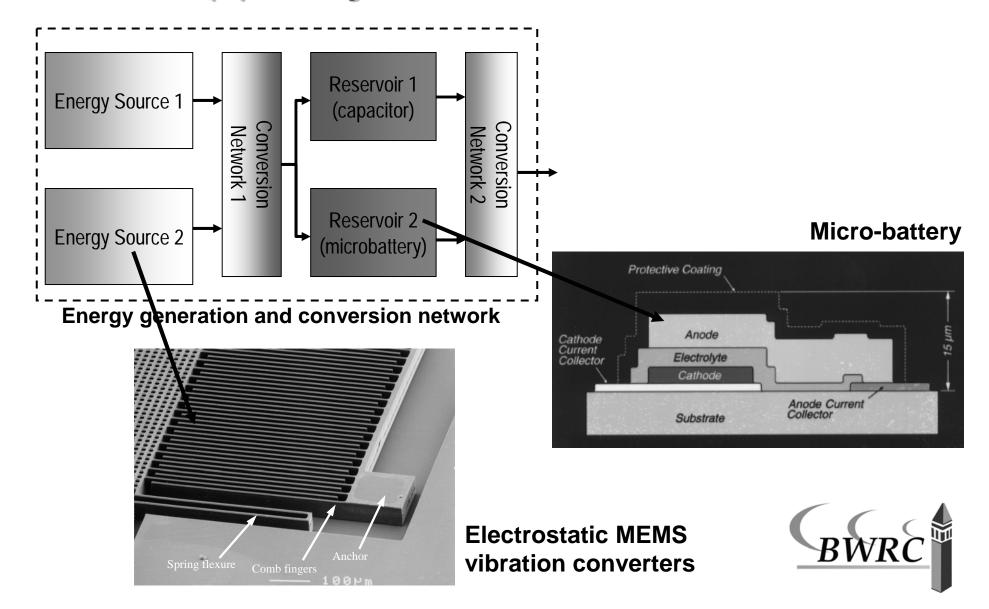

#### A Longer Term Perspective: On chip power generation and conversion networks

#### Summary and Perspectives

- Active and static power management is leading to a fundamental change in the concept of power distribution on a chip

- Power domains locally manage and trade-off performance, leakage and process variance

- System supervisors giving new meaning to the term OS

- Towards "PGE on a chip"