# MP System-on-Chip: Embedded Test, Diagnosis and Repair in Practice

Yervant Zorian

Virage Logic Corp

zorian@viragelogic.com

#### **Contents**

- Introduction

- SoC yield & reliability challenges

- Optimization loop concept

- Infrastructure IP & resource partitioning

- Examples of embedding infrastructure IP

- Conclusions

#### Introduction

- Cost

- reduce semiconductor fabrication cost by improving manufacturing yield

- Time-to-Volume

- Short time to market and short product lifecycle

- faster yield optimization impacts market entry time and bottom line

- Quality

- Production of high quality manufactured silicon

### **Deep Submicron Trends**

- Number of transistors

- Mixed technologies

- Shrinking geometries

- Process layers

- New process material

- High performance

### **Deep Submicron Impact**

- Miniaturization and High Performance result in

- Finer and denser semiconductor fabrication

- Increased susceptiblity

- Increased defectivity

- Lower manufacturing yield and reliability

- Observed as

- Defect density

- Realistic Faults

- Timing problems

- Transient or Soft Errors

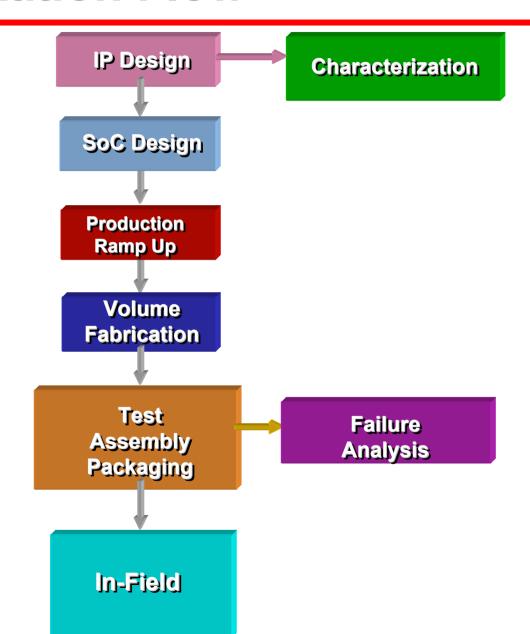

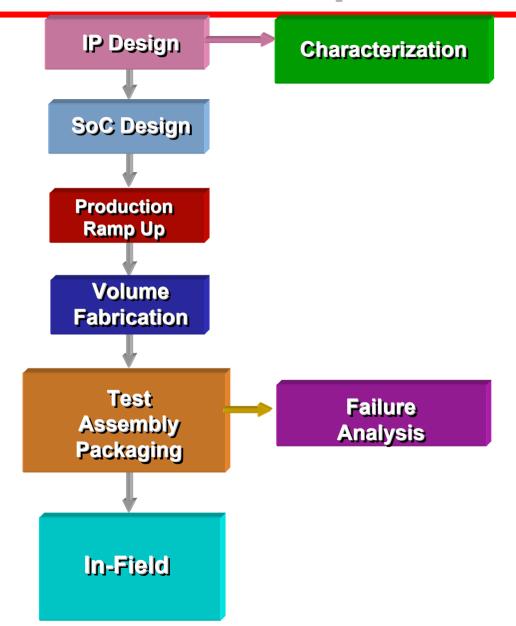

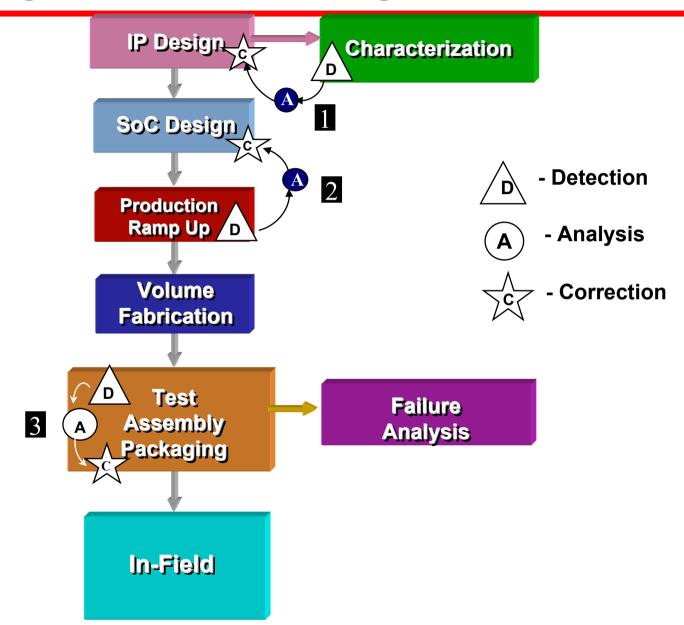

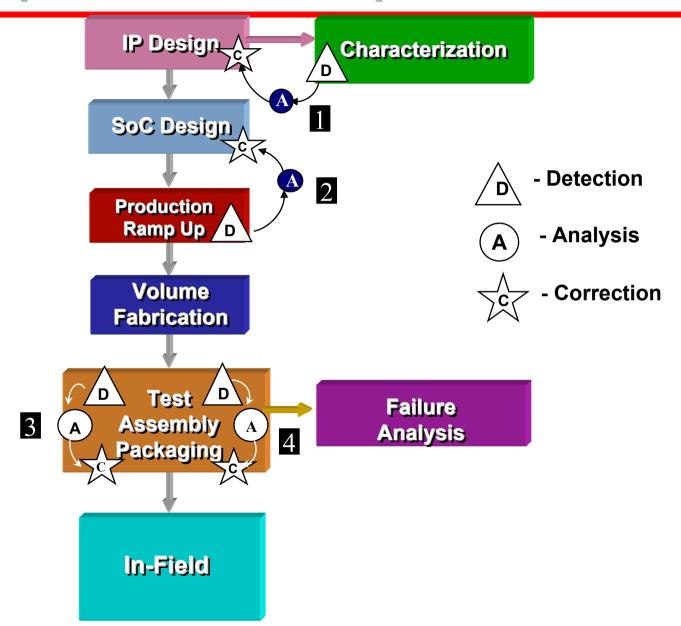

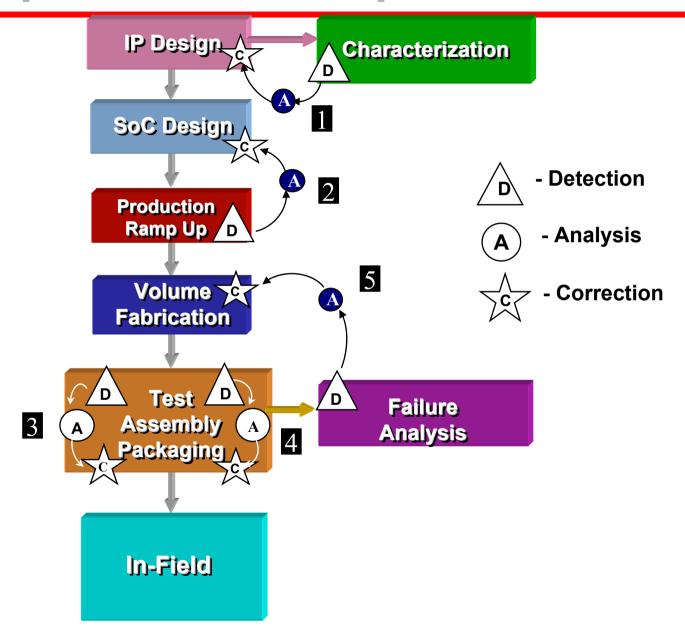

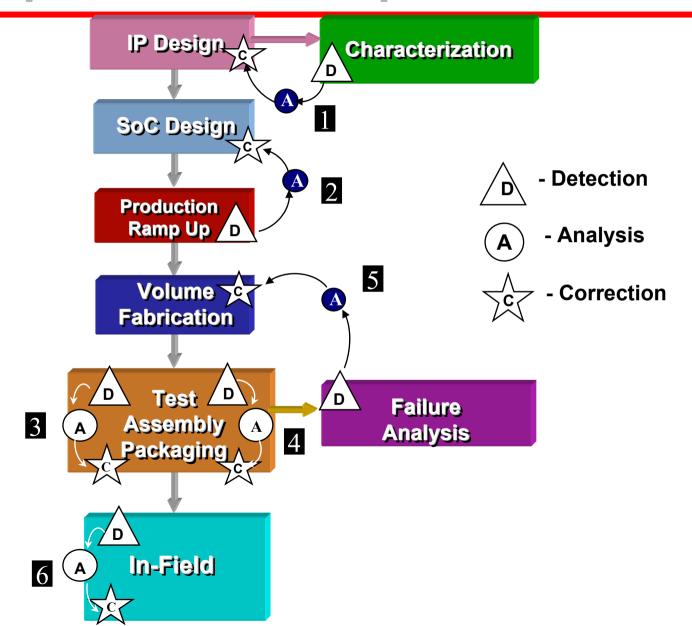

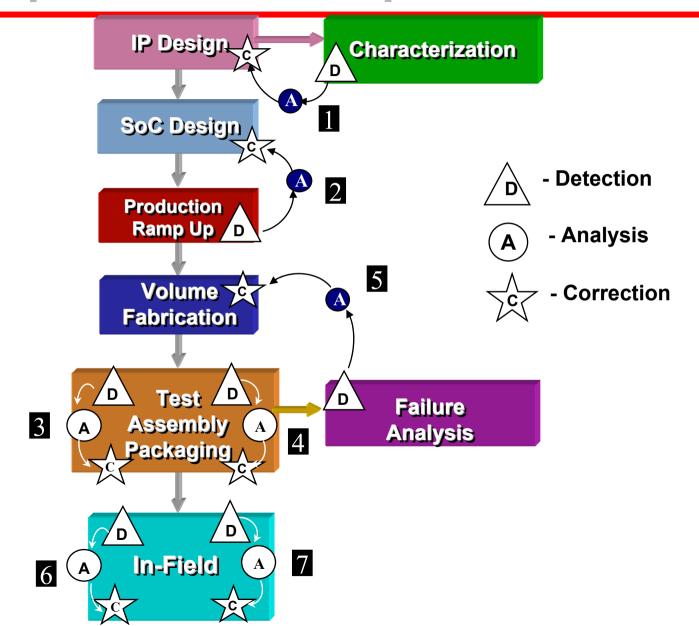

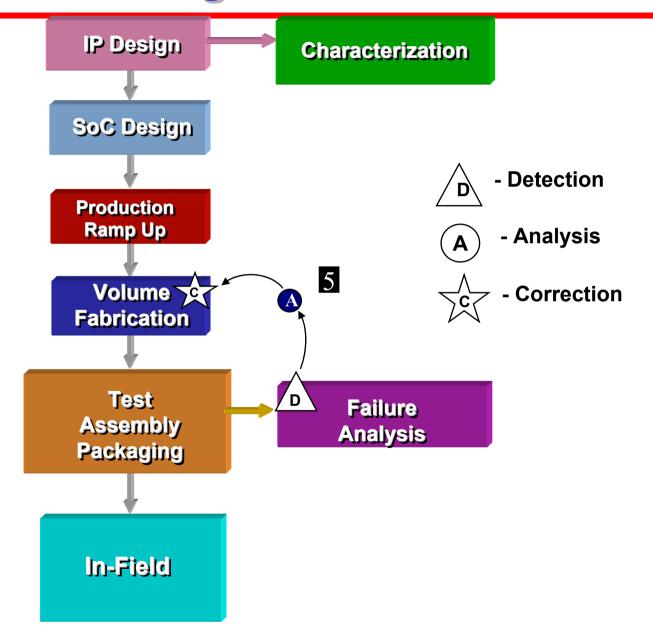

#### **IC Realization Flow**

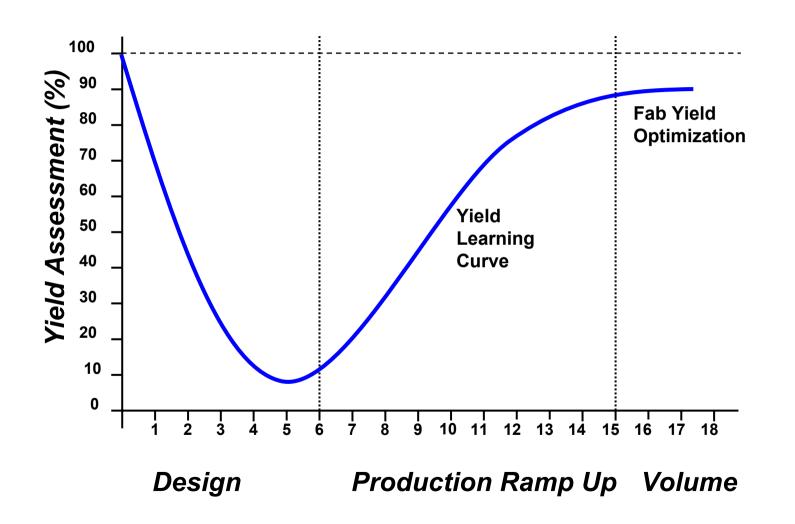

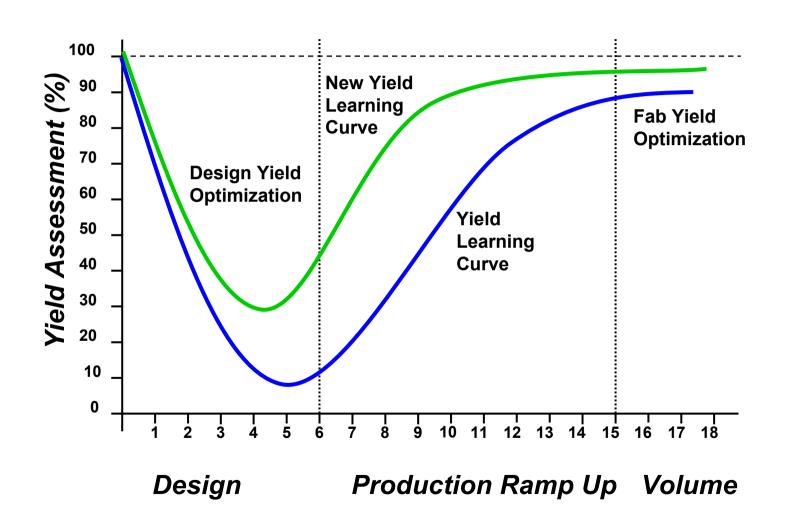

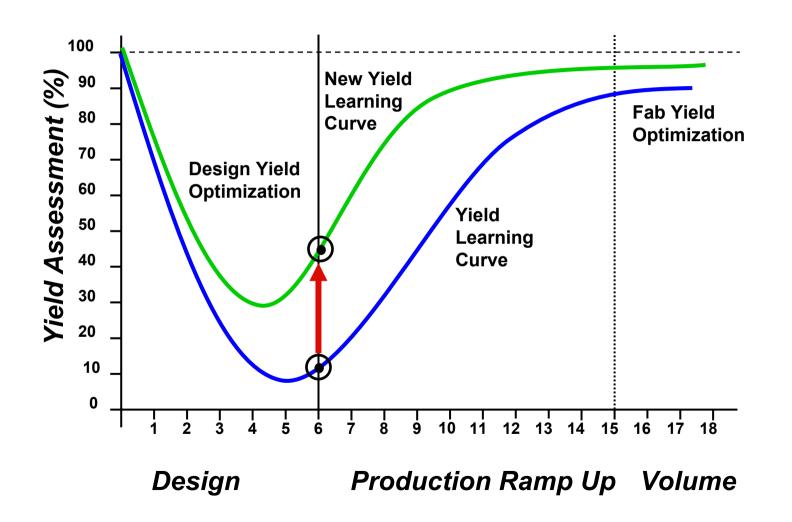

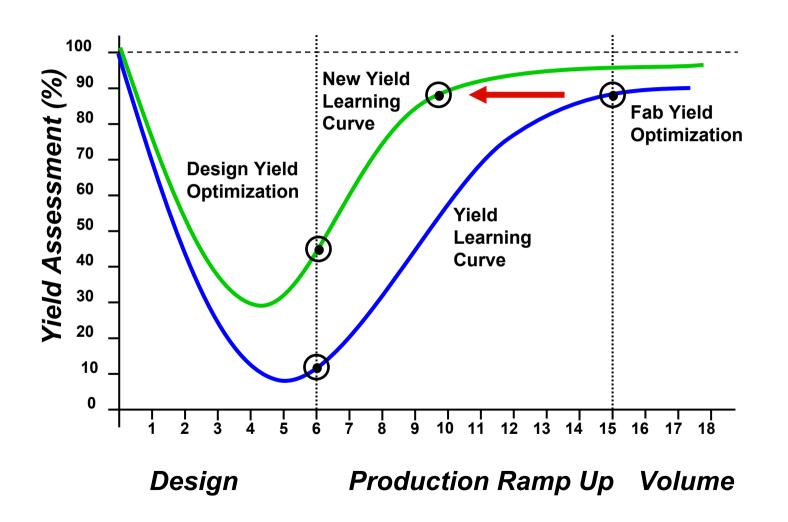

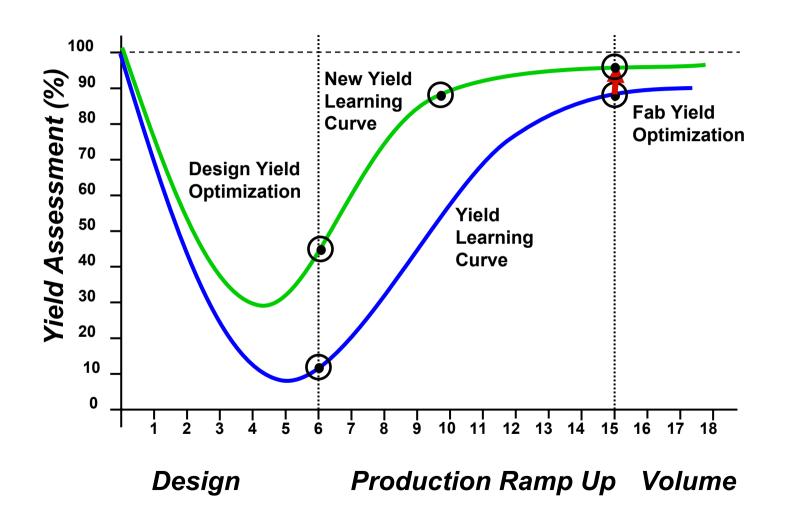

### 1. Yield Learning Challenge

- Semiconductor process evolving and introducing new material and techniques

- result in new generation of yield limiting factors

- Small geometries

- result in devices more susceptible to systematic and random defects and higher defect densities per layer

- Increased time-to-market pressure

- result in chip volume production at lower yield level

- Disaggregated semiconductor industry

- result in F-IP providers assuming yield optimization responsibility

- Need process monitor IP and yield prediction and optimization for each new design (IP and SoC)

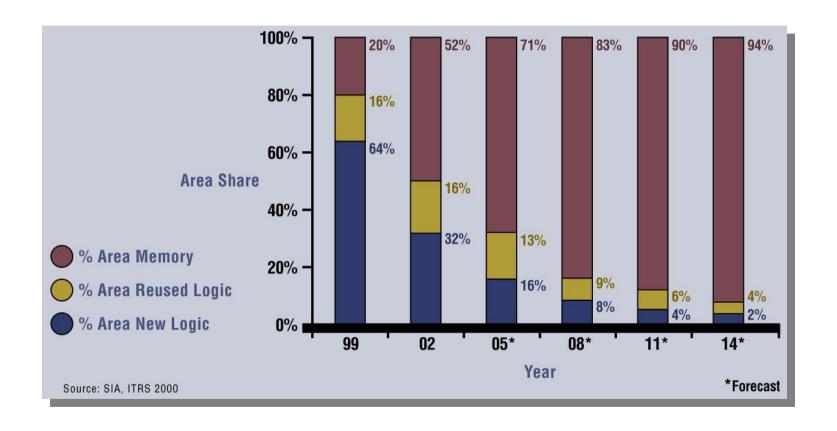

# 2. Embedded Memory Challenge

# 2. Embedded Memory Challenge

# 3. Failure Analysis Challenge

- Traditional physical failure analysis steps -

- Fault localization

- Silicon de-processing

- Physical characterization and inspection

- Small geometries result in

- Finding smaller more subtle defects

- Tighter pitches require greater spatial resolution

- Backside analysis due to metal layers & flip-chip

- Need to gather failure data using diagnosis IP and analyze obtained data by off-chip fault localization methodologies and tools

# 4. High Performance Challenge

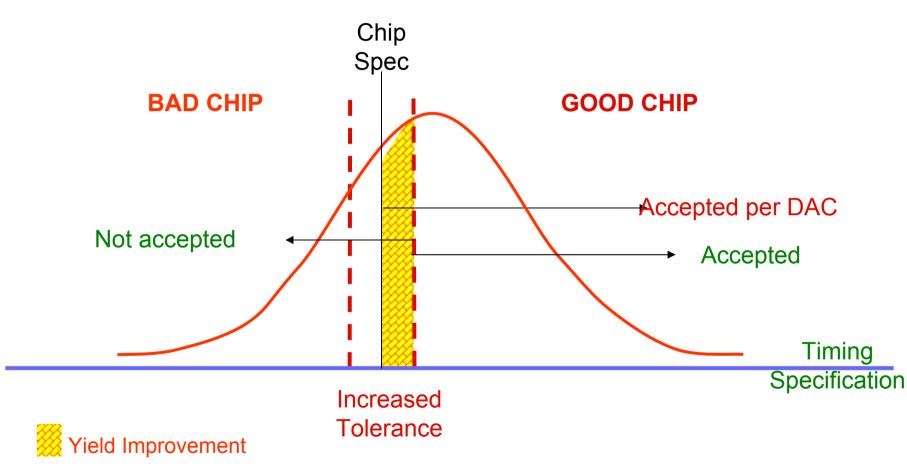

- Increased performance require increased accuracy for proper resolution of timing signals

- Semiconductor off-chip speed improved 30% per year, test accuracy improved 12% per year

- Tester timing errors approaching cycle time of faster device

- Yield loss due to tester inaccuracy (extra guardbending performed at test stage)

- Need for measuring and analyzing time specifications using embedded timing probes with high accuracy

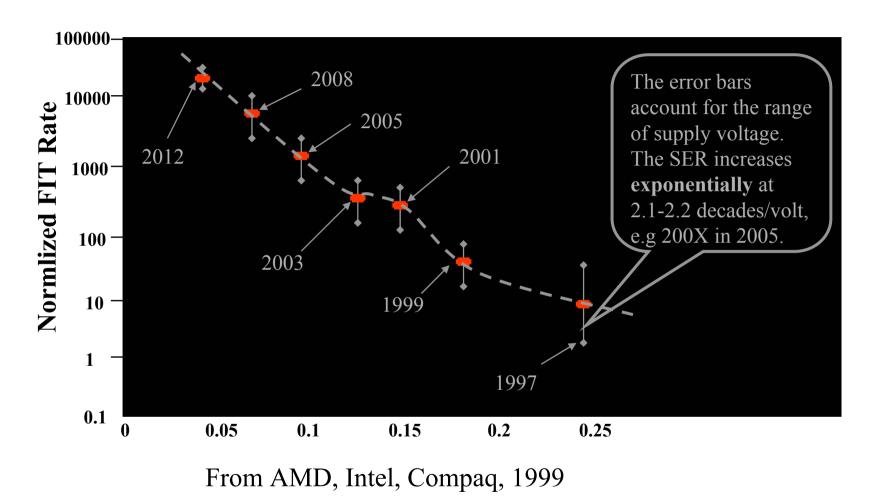

### 5. Transient Error Challenge

- Smaller geometries and reduced power supplies result in reduced noise margins

- Soft errors, timing faults, crosstalk are major signal integrity problems

- SoC needs self correcting, i.e. embedded robustness, engine in order to resist to this challenge

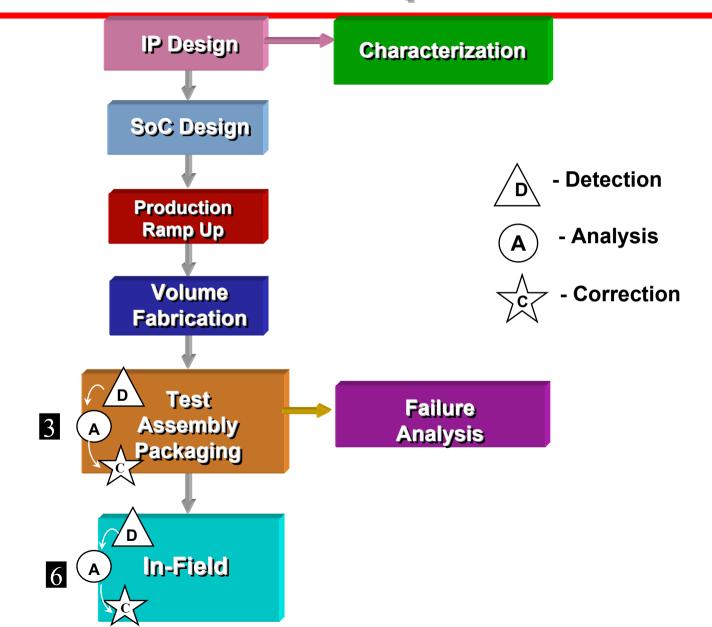

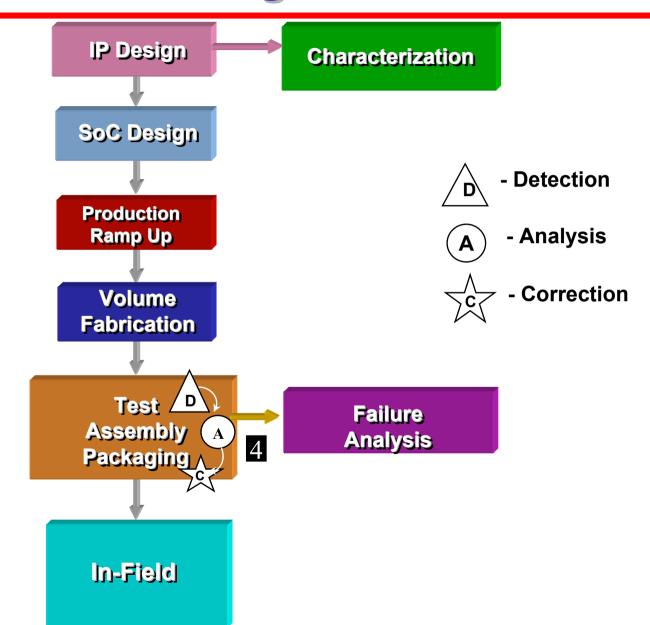

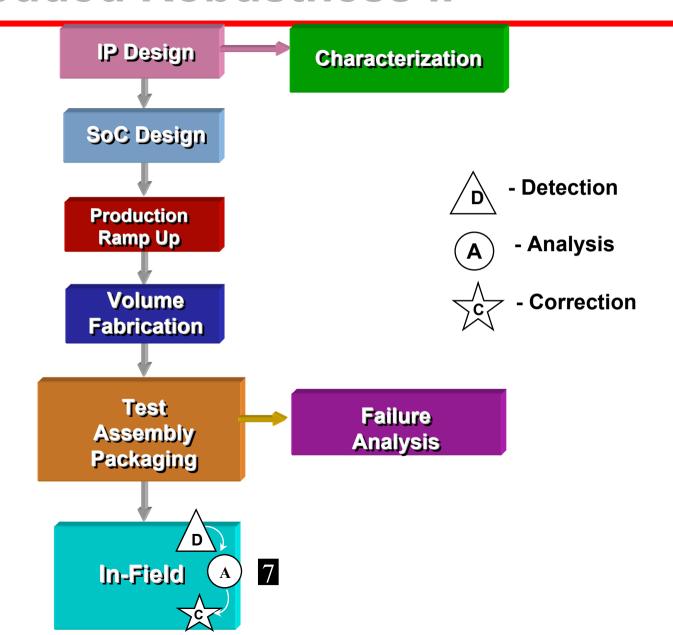

- Need for Advance yield optimization solutions

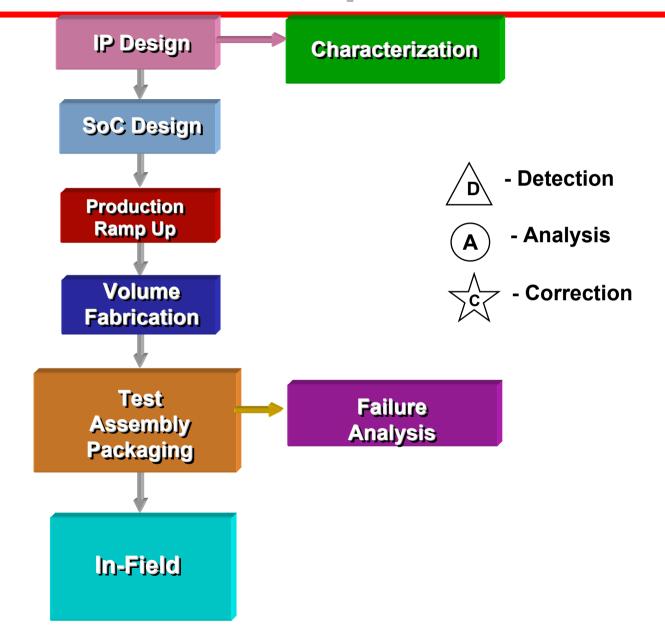

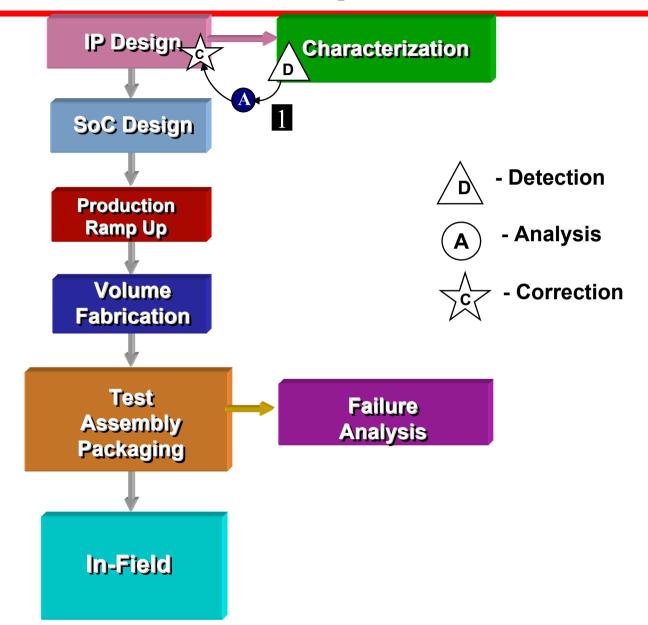

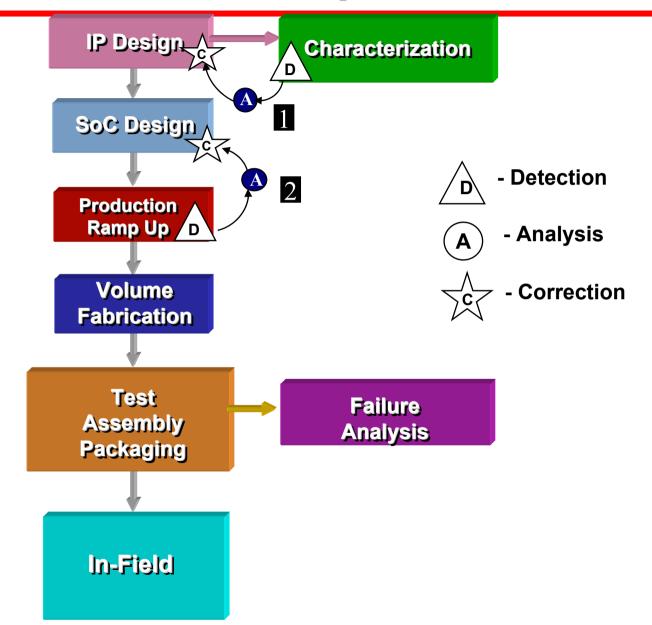

- Introduced at different stages of chip realization flow

- Yield optimization feedback loops comprised of three steps

- Detection, Analysis, Correction

- Three step loops either reside completely off-chip, partially on-chip/off-chip or embedded on-chip

- Examples of yield optimization feedback loops

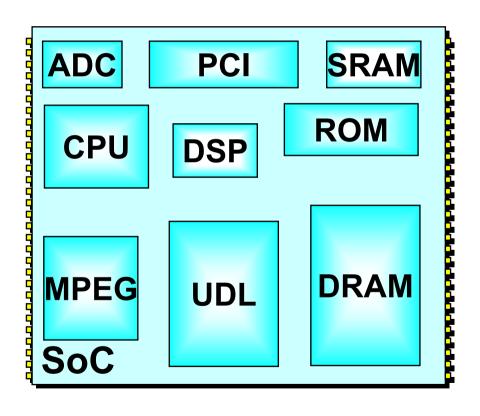

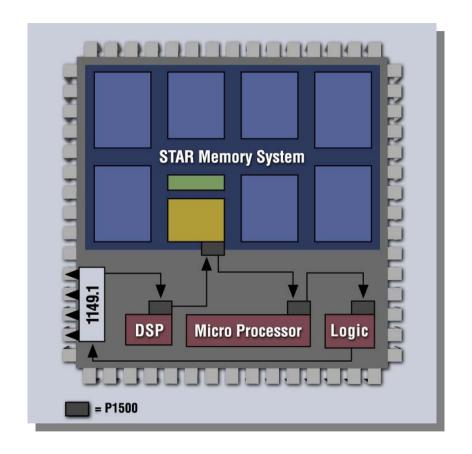

#### **Functional IP in SoC**

# Multiple Functional IP (F-IP) types have been absorbed into single SoC design

#### Infrastructure IP in SoC

- Transparent to normal functionality of SoC (not functional IP)

- Ensures manufacturability and lifetime reliability of SoC

- Basic types of Infrastructure IP include:

- IP for process monitoring

- IP for testing

- IP for diagnosis and debug

- IP for repair

- IP for characterization & measurement

- IP for robustness and fault tolerance

#### Infrastructure IP in SoC

- Infrastructure IP absorbed into Soc design

- External equipments and sensors

- Embedded I-IP on Wafer

- Embedded I-IP at SoC level

- Embedded I-IP distributed over F-IP

- Embedded I-IP integrated into F-IP

- Resource partitioning and I-IP at multiple levels

- Examples of Embedding I-IP to create YOL

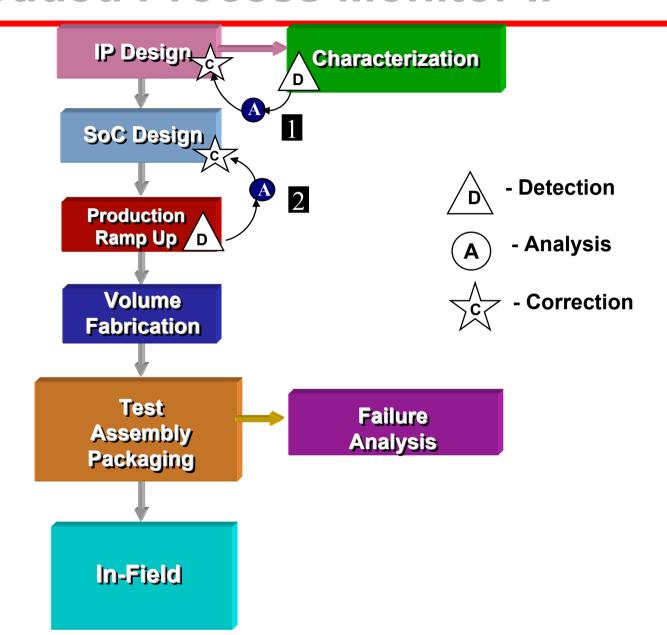

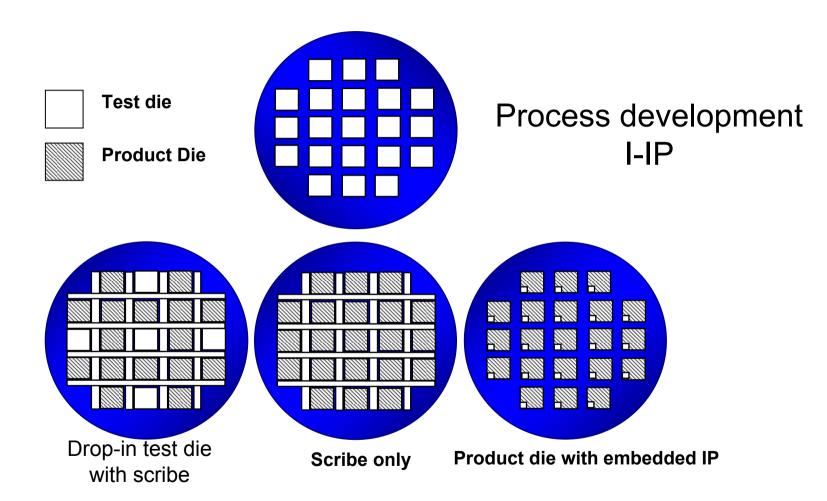

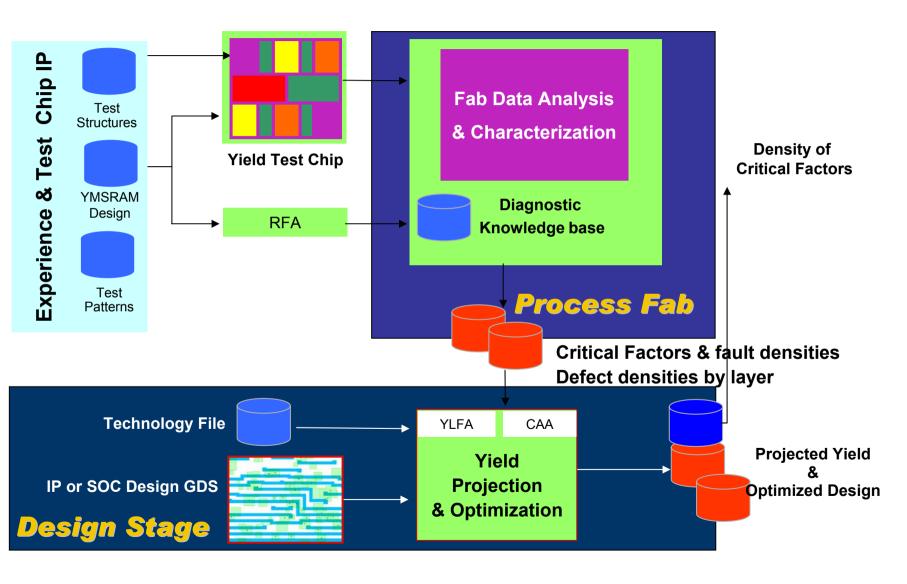

#### 1. Embedded Process Monitor IP

#### 1. Embedded Process Monitor IP

- Passing DRC does not guarantee high yield

- D-component of feedback loop is I-IP

- Monitor process characteristics

- Collect device attributes

- Known as: test vehicle or test die

- Process Monitor IP used during process development and/or later during production

- Process Monitor IP may be test die (full chip), scribe or embedded IP in SoC

#### 1. Embedding Process Monitor IP

Source HPL Technologies

# 1. Embedded Process Monitoring IP

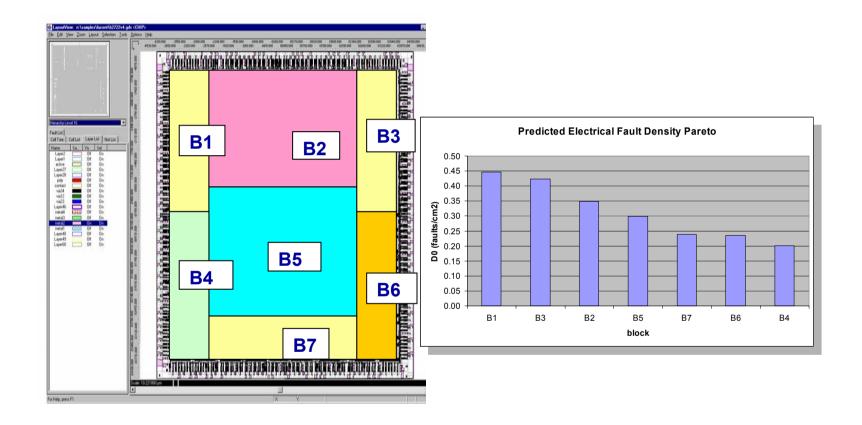

- Use information and knowledge about process to predict yield of a given design (IP or SoC) before it is committed to silicon (A- component)

- Identify weekest links in design

- Block, IP, layer, design structures

- Yield Optimization: improve design (IP or SoC) by modifying week links at GDS level (C- component)

### 1. Using Process Monitor IP

### 1. Using Process Monitor IP

# 2. Embedded Test & Repair IP

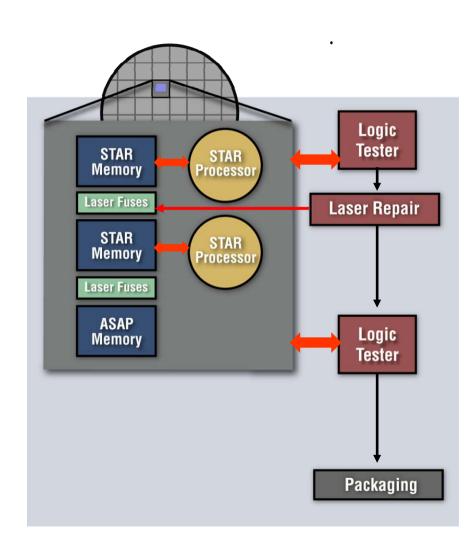

## 2. Conventional Manuf. Repair

- External Test & Repair Method

- Store failed bit map externally in a large capture memory

- Use external general purpose redundancy allocation software

- Blow fuses using external repair equipment

- High cost and silicon area

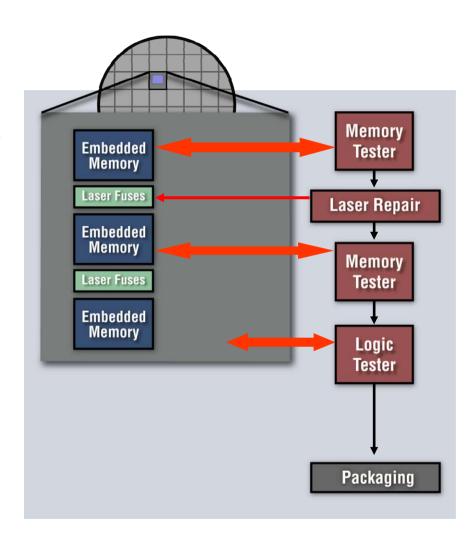

# 2. I-IP for Single Time Repair

- External Memory tester eliminated

- External bit map storage eliminated

- External redundancy analysis software eliminated

- High yield achieved because of integrated solution

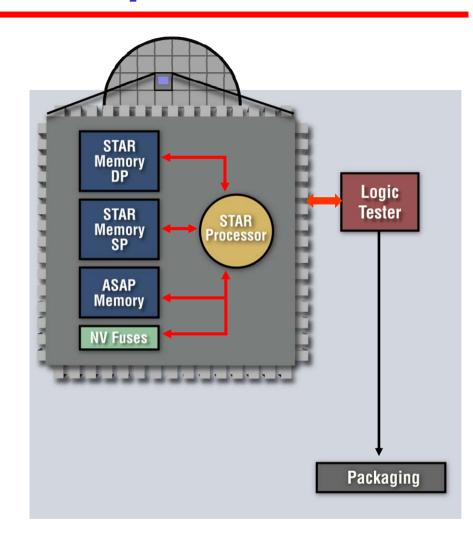

## 2. I-IP for Multi-Time Repair

- External repair equipment eliminated

- Overall manufacturing cost reduced

- Efficiency of repair increased (PVT corner conditions repaired)

- Efficient of area & performance improved

#### 2. Distributed I-IP for ET&R

- Built-in memory self-test

- Defect Analysis

- Redundancy allocation

- Repair

- Reconfiguration data download

- Retest

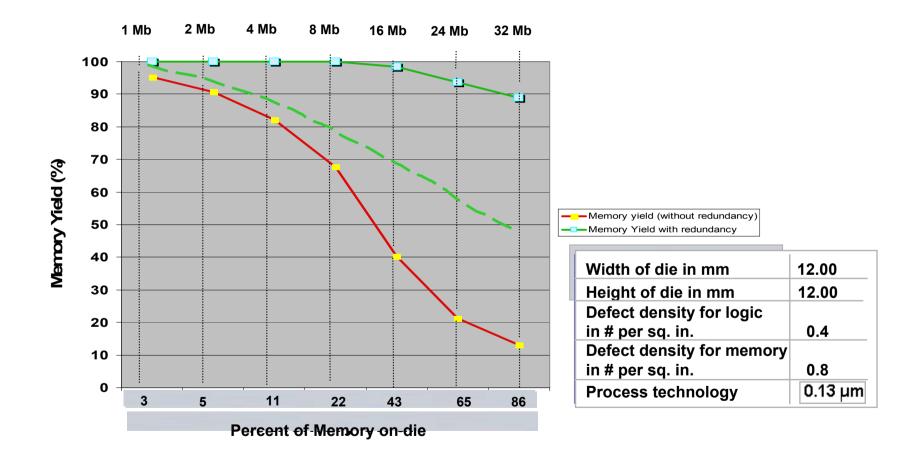

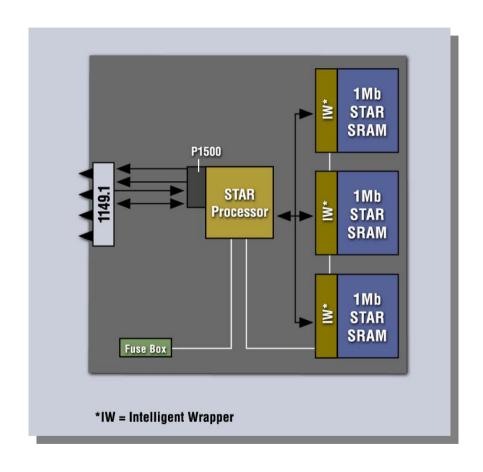

# **Composite IP for Embedded Memories**

# 2. Quality & Reliability: Design

- Highest defect coverage

- Very deep submicron impact on defectivity in embedded memories

- Highest repair efficiency

- Complex redundancy mechanisms

- Fault Detection and Localization Algorithms

- Reconfiguration Mechanisms

- Redundancy Allocation Algorithms

- Repair Methodology

# 2. Time-to-Market: Design

- Pre-Integrated F-IP and I-IP into a single SIP autonomous entity

- Interoperability: use of standard interface to I-IP, such as P1500

# 3. Embedded Diagnosis IP

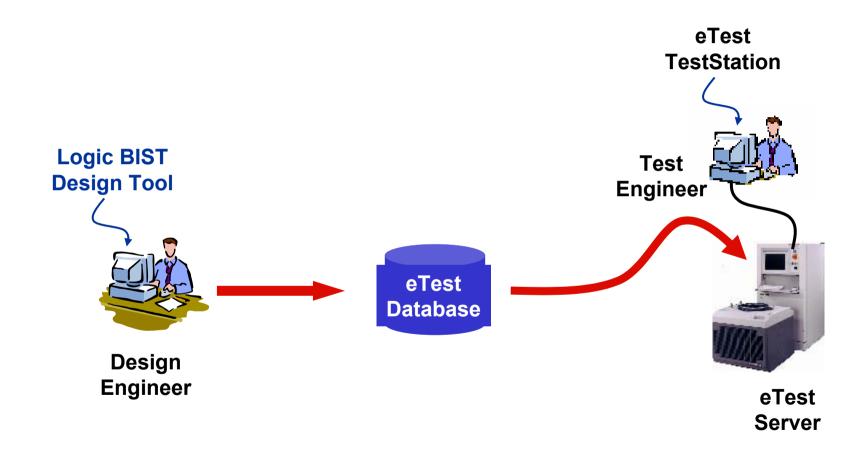

## 3. Embedded Diagnosis IP

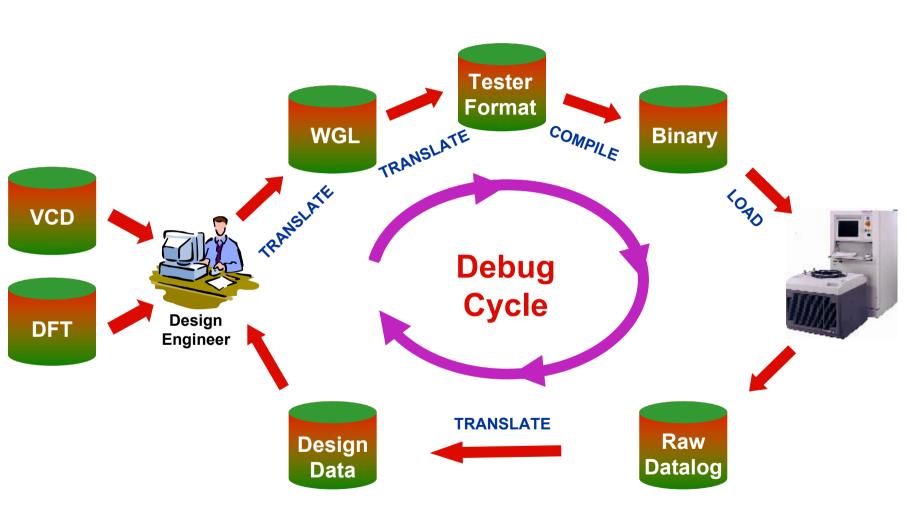

- Need to gather failure data using diagnosis IP and analyze obtained data by off-chip fault localization methodologies, tools and equipment

- Leverage same infrastructure IP for test, silicon debug and diagnosis

- Integrated Silicon Debug Solution comprised of -

- Analysis & generate embedded test & diagnosis IP

- Integration & simulation of embedded test & diagnosis IP

- Creation of embedded test database

- Failure data from diagnosis IP analyzed off-chip for fault localization

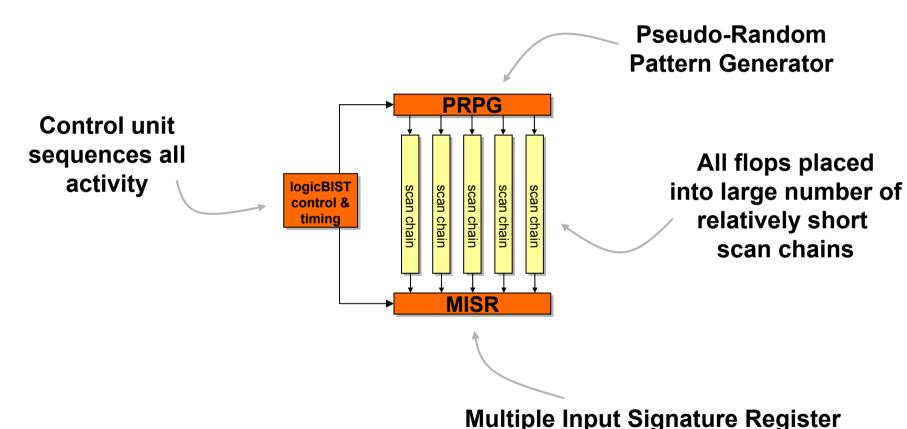

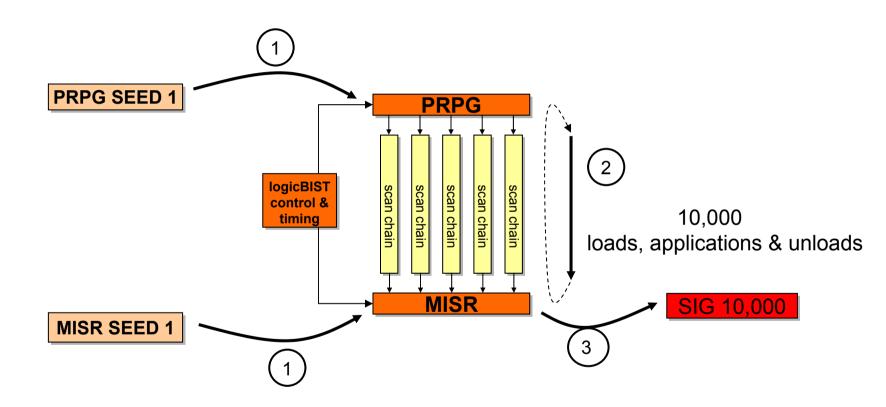

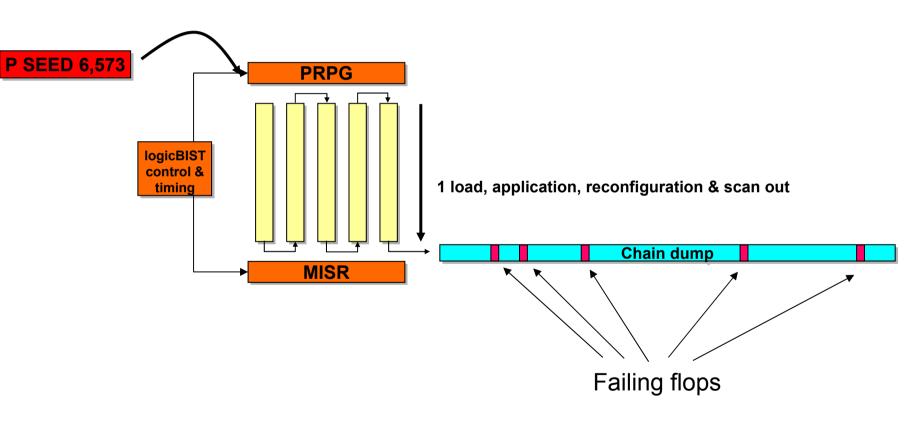

# 3. Infrastructure IP for Logic BIST

compresses responses into a signature

Source LogicVision

## 3. Logic BIST Test Sequence

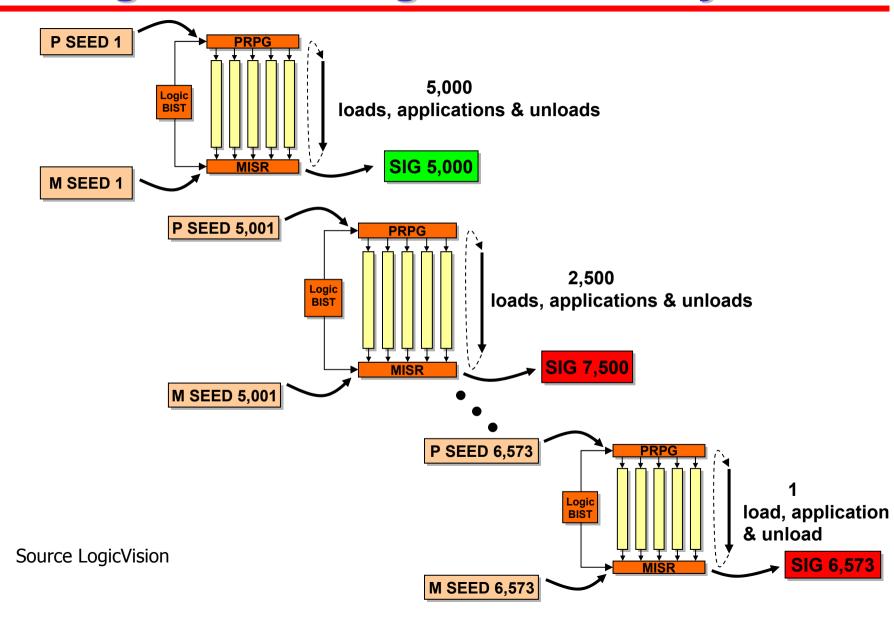

# 3. Logic BIST Diagnosis- Binary Search

# 3. Logic BIST Diagnosis-Binary Search

Source LogicVision

# 3. Conventional Diagnosis Flow

# 3. Integrated Diagnosis Solution

# 4. Embedded Timing IP

# 4. Embedded Timing IP

- Very stringent timing specification

- Difficulty in obtaining accurate measurements using external instrumentation

- Embedded timing IP [Tabatabaei 02] comprised of

- Multiple high speed probes

- Embedded control core directs probes and transfers information to timing processor for analysis

- Yield gain obtained due to accurate measurement

# 4. Yield Gain due to Timing IP

Source: Vector 12

#### 5. Embedded Robustness IP

# 5. Field Reliability Challenge

#### 5. Soft Error Risk

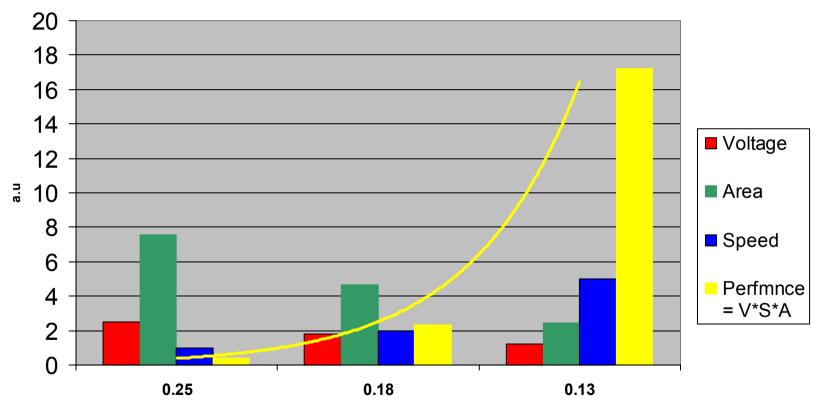

➤A 0.13µm design offers **40X** more performance than 0.25µm

... but is **40X** more prone to Soft Errors

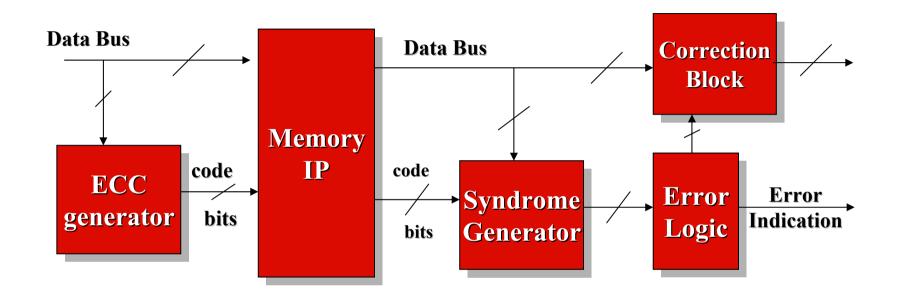

#### 5. Robustness IP for ECC

Standard ECC architecture provides single bit repair and adds extra delay to each read and write operation

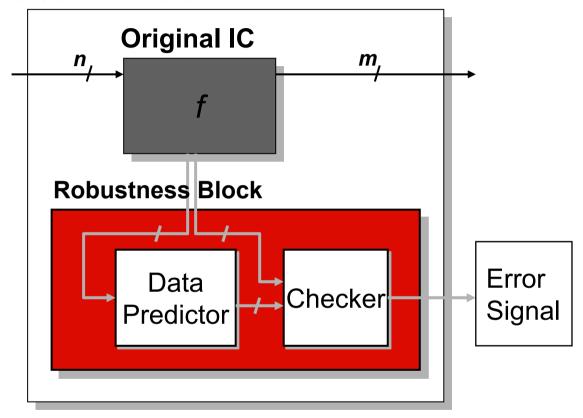

# 5. Robustness IP for Random Logic

#### **Protected Function**

Source: iRoC Technologies

#### Conclusions

- Leveraging I-IP for higher yield and reliability

- Leveraging I-IP for Time-to-Volume Acceleration

- Infrastructure IP may require external support, automated tools and equipment

- Yield optimization loops leveraged at different product realization steps during design, fabrication, test and in-field

- Collaborative Environment is necessary to achieve Yield, Quality and TTV goals

# THANK YOU FOR YOUR ATTENTION