### The Use Of Virtual Platforms In MP-SoC Design

Eshel Haritan, VP Engineering CoWare Inc. MPSoC 2006

# **MPSoC**

### Is MP SoC design happening?

### Why?

TEXAS INSTRUMENTS TECHNOLOG

$\cap$

### .....and it comes in many flavors

# Agenda

- MPSoC Solution Space

- Virtual HW Platforms

- What are Virtual Platforms?

- Virtual Platform usage for Architectural Exploration

- Virtual Platform usage for SW development

- Requirements from Virtual Platforms

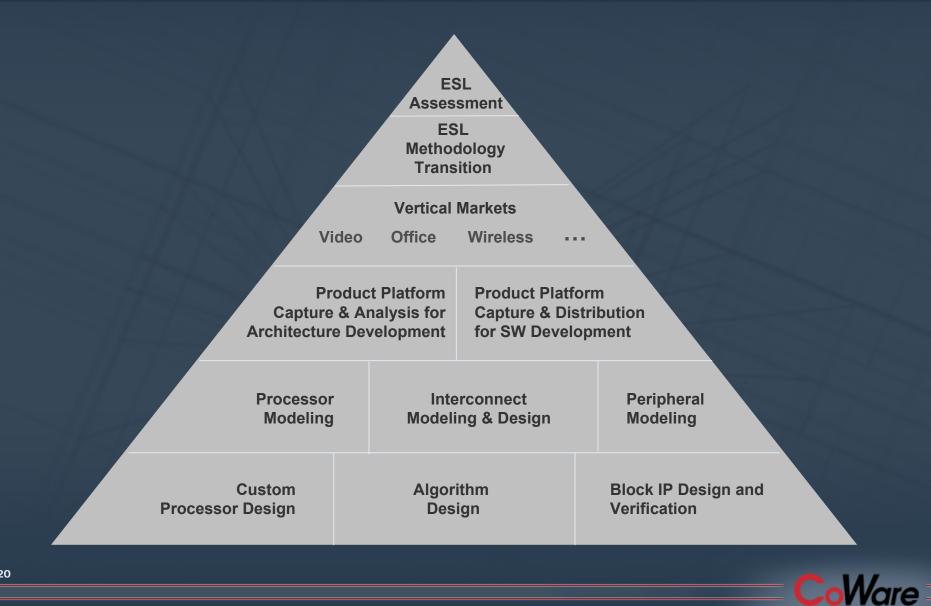

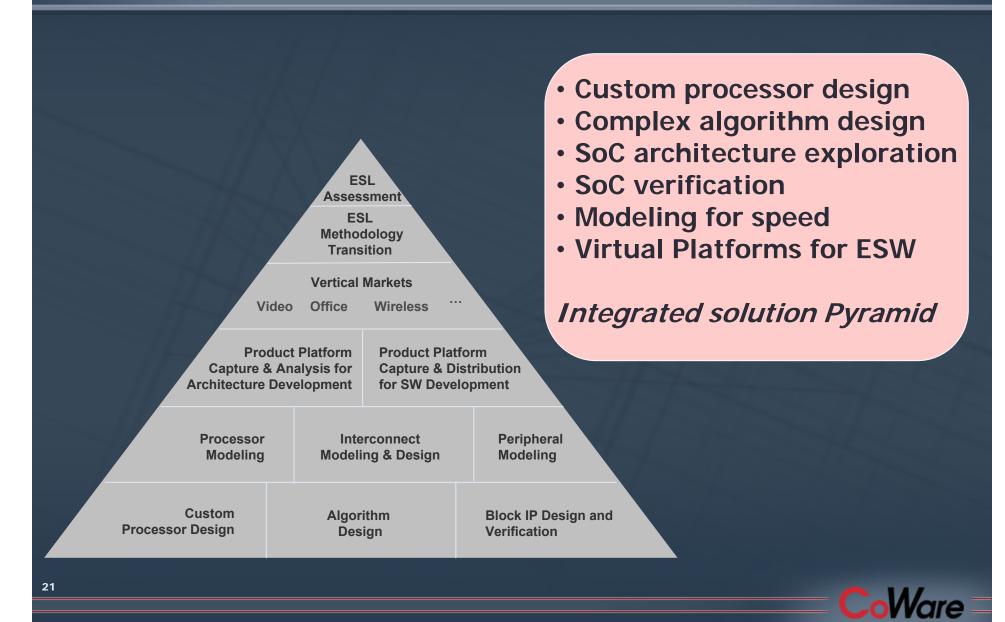

- The ESL Solution Pyramid

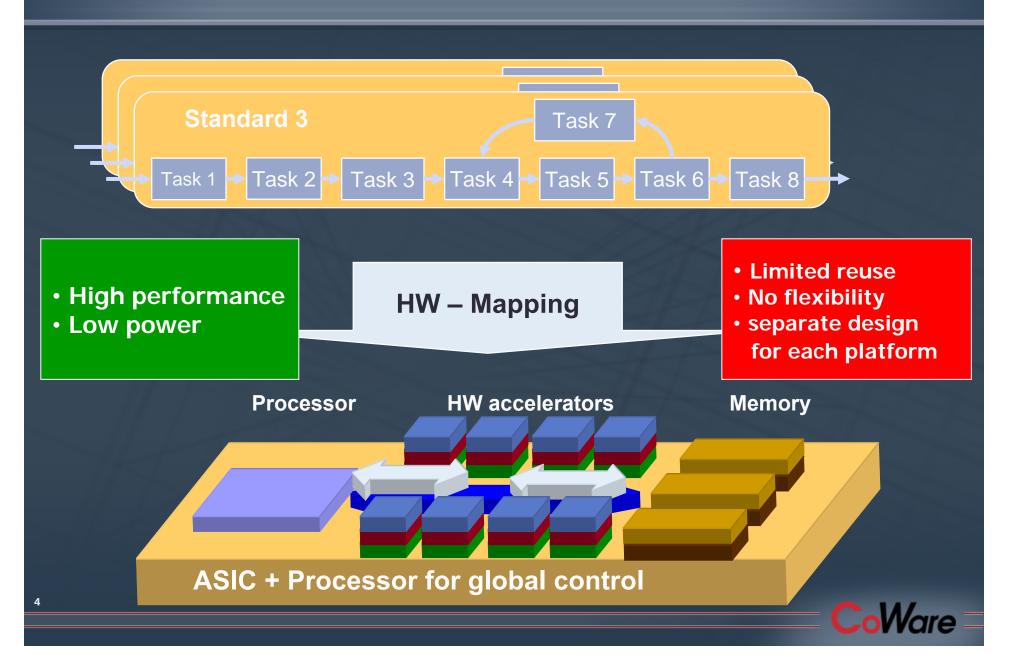

## **Solution Space: HW Implementation**

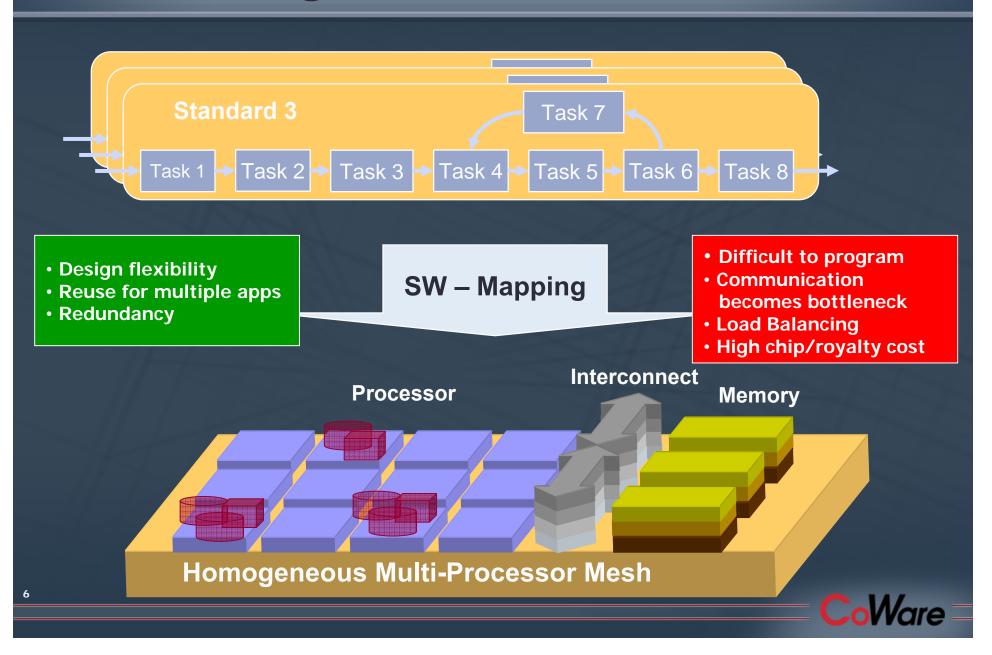

## Homogeneous MP-SoC Mesh

#### **Solution Space: Heterogeneous SoC Standard 3** Task 7 Task 6 Task 1 Task 2 Task 3 Task 4 Task 5 Task 8 SW – Mapping Reuse of legacy design Load balancing Reuse of legacy SW Memory sub-system design Task 1 **Task 6/7** Task 8 Task 3/4/5 **HW Accelerator** Accelerator **Processor** Task 2 Accelerator + Ctrl **Accelerator** Mem Mem Mem **Heterogeneous Multi-Processor SoC** 7

# The ESW View

### User-Level Functions (Applications, UI)

**GOPS** Middleware (Algorithm)

### "Board Support Package"

User Interface, User level functions Large ESW stack >10 Million lines of code C, C++, Java Soft real time - Defined by user perception Cache, MMU Use generic components for data movement Generic bus arbitration + peripherals

#### Algorithm rich

Small ESW stack ~1 Million lines of code C, C++ (no Java), or assembly, or Matlab Hard Real Time Cache off, MMU off Smart DMA, guaranteed Quality of Service Data locality NoC, guaranteed QoS, predictable latency Dedicated communication channels

Hardware abstraction Layer + OS Support Thin layer ~100K lines of code C with inline Assembly, maybe C++ Accurate Response Time

MOPS

**KOPS**

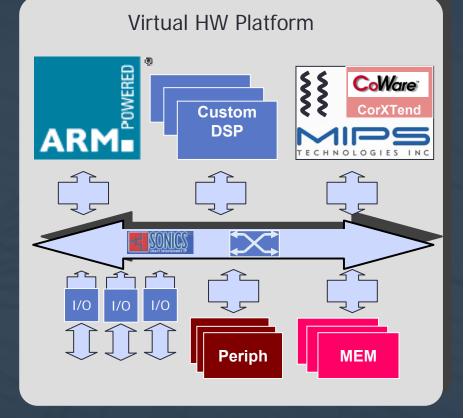

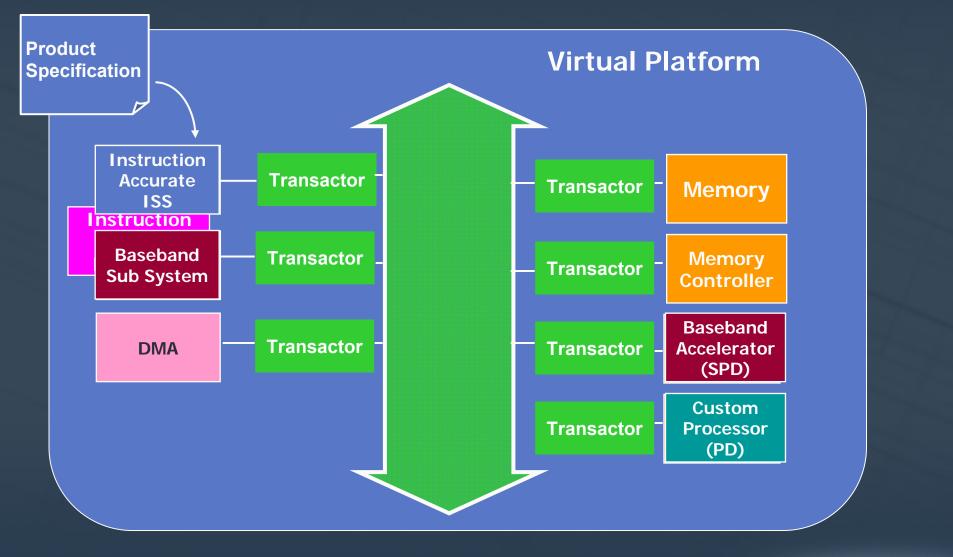

# What is a Virtual HW Platform?

- A SW model of the SoC HW

Processors, accelerators, peripherals and interconnect

HDS – HAL, Drivers, O.S., I/O

- Enables architecture exploration and optimization

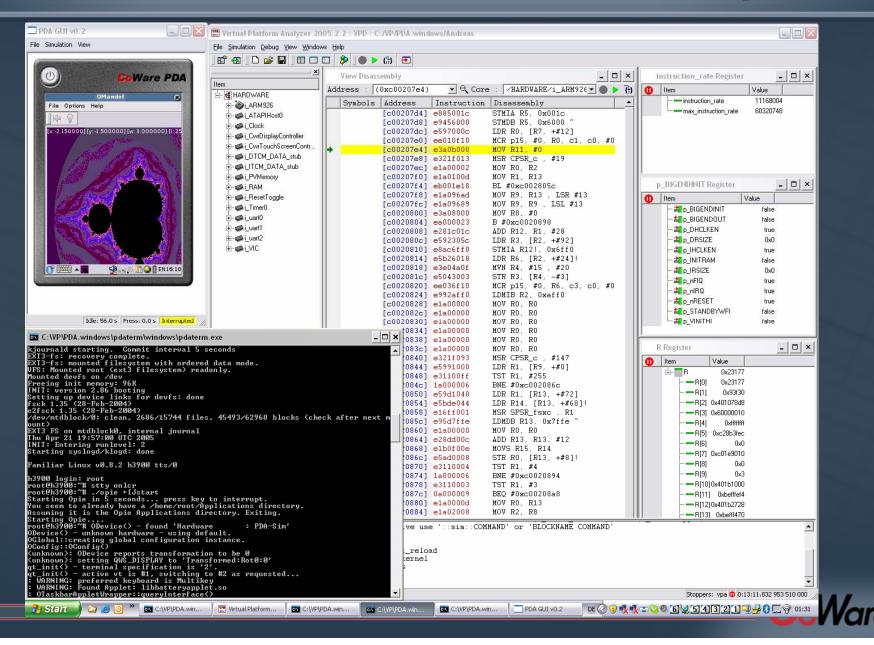

- Enables ESW development, debugging and optimization

- Different abstraction levels for different use models

# Virtual HW Platform Value

### Fast

- Allows accuracy-speed trade offs

- Flexible

- Cost effective

- Scaleable

- Observable and Controllable

- Available early in the design cycle

## Virtual HW Platform Value

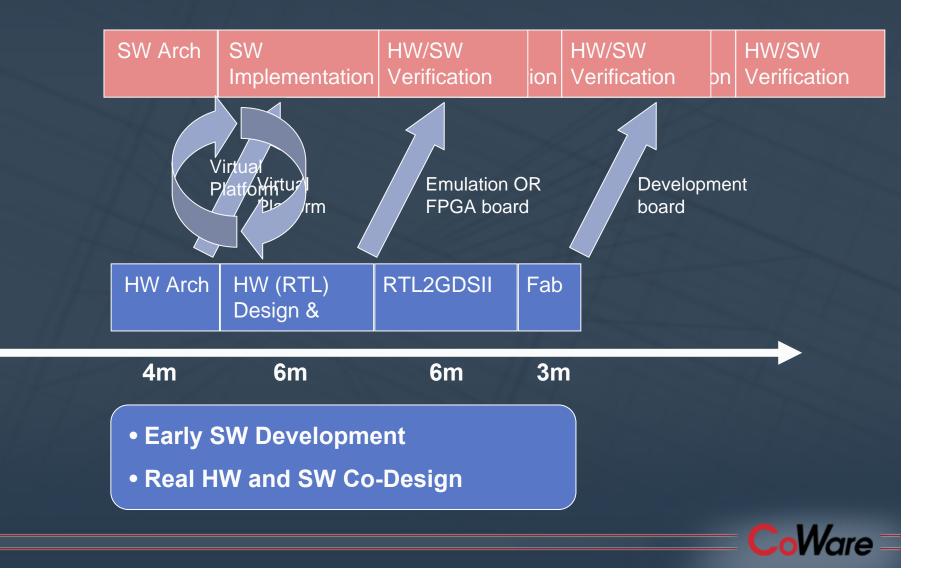

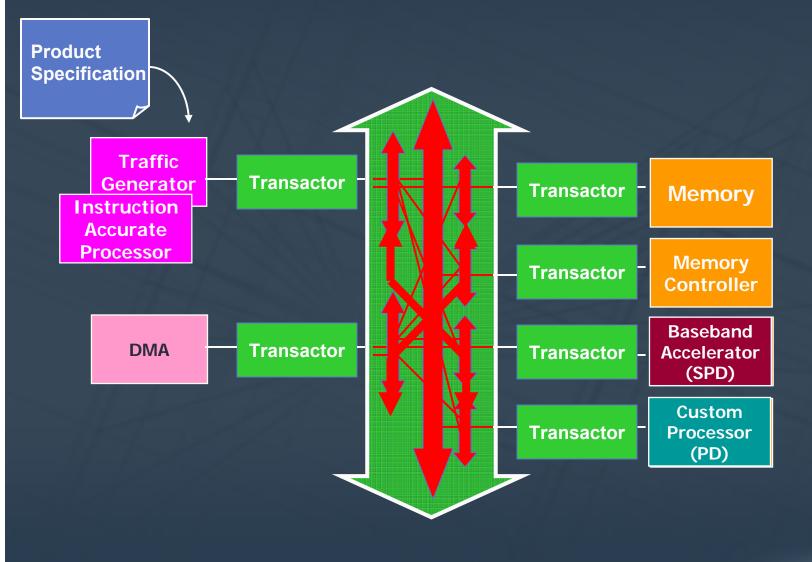

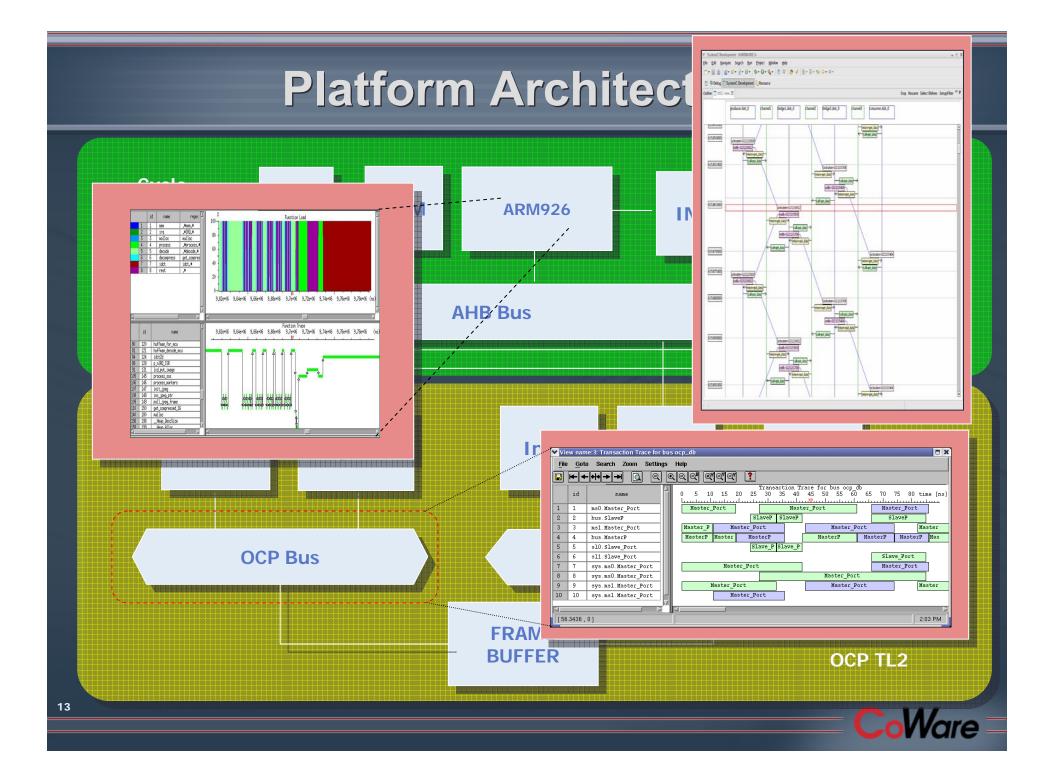

### Virtual HW Platform for Architecture Exploration

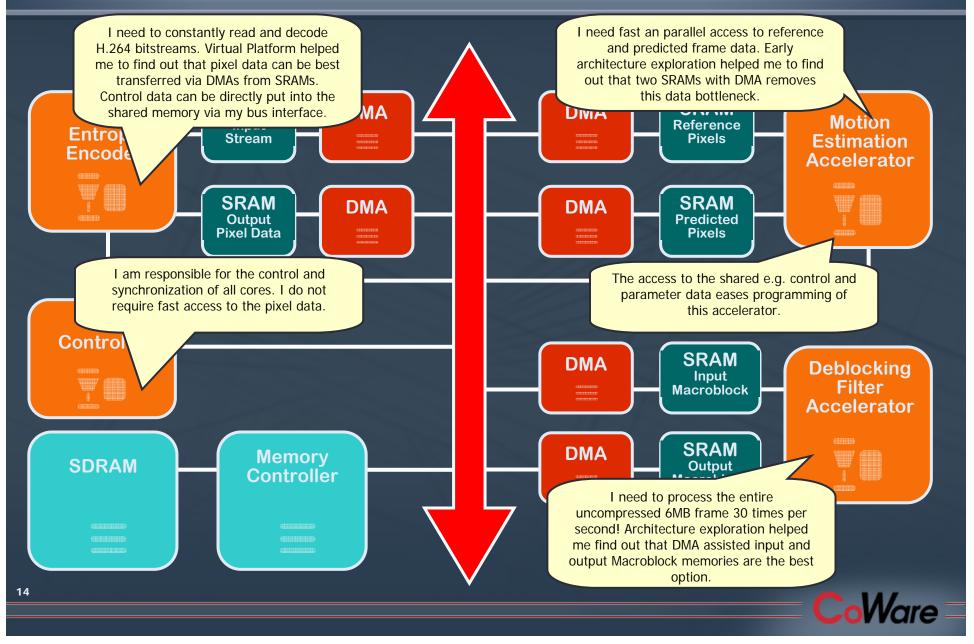

## Virtual Platforms for Architecture Exploration

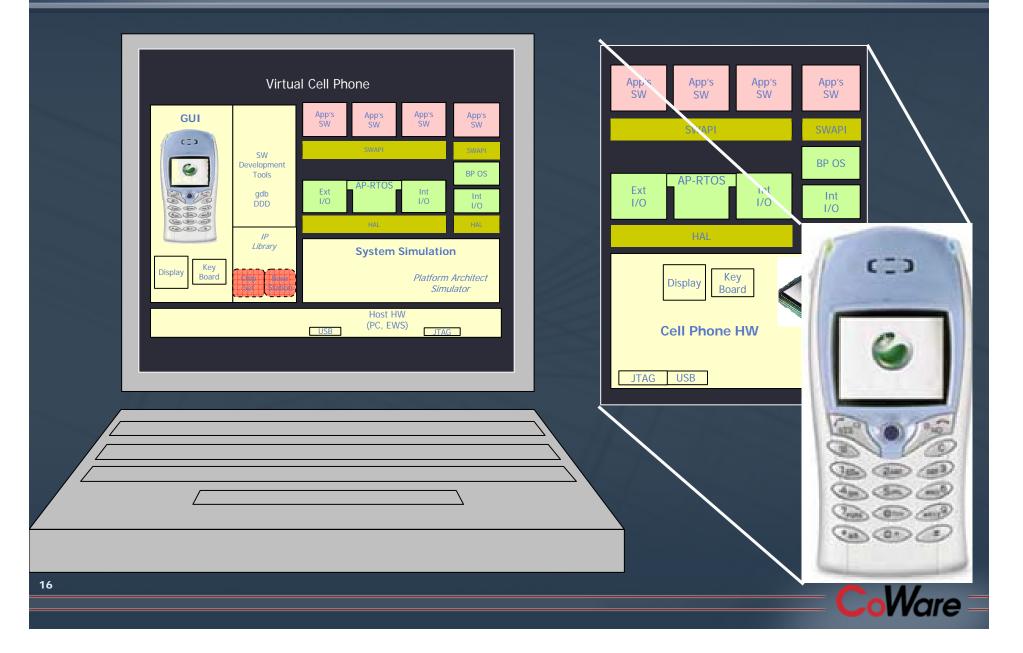

### Virtual HW Platform for ESW Development

### **Virtual Platforms for ESW Development**

### Virtual HW Platform for ESW development

## Virtual Platform – What is Required?

- Ultra fast processor simulator ISS

- Accuracy-speed trade-offs

- Library of fast processor models

- Explore different communication paradigms

- Strong analysis solutions

- Library of communication protocols

- Integrate DSP algorithm

- Library of popular Wireless and MM standards

- Ultra fast platform

- Accuracy-speed trade-offs

- Multi core and platform debugging

- Standard based

# Why Standards Based?

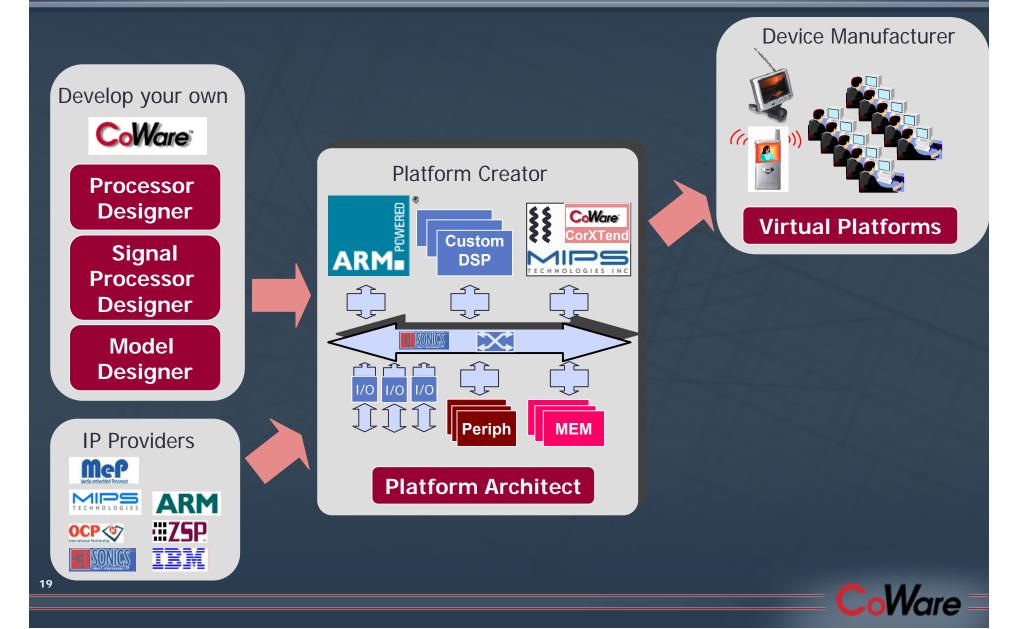

# **Solutions Pyramid**

## Summary

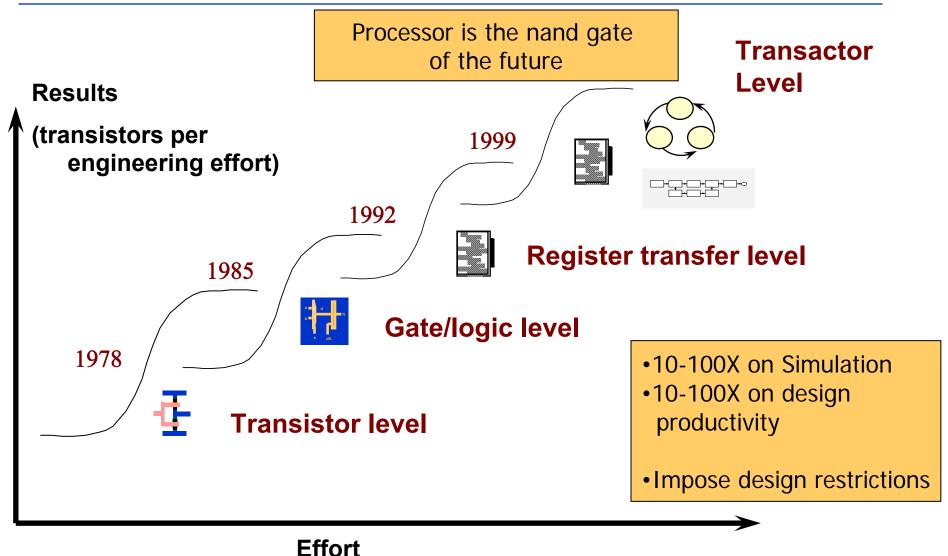

## So what's the next level of abstraction?

# The Next Level Challenge

- The next level is (maybe):

- Processors and HW accelerators

- SW tasks running on these processors

- Transaction level modeling to model communication

- What are the design restrictions we need to impose to gain 100X productivity?...and what are the benefits to the users?

- Processors

- Simplify? No Cache? No MMU? Speculative execution? Branch prediction?

- SW tasks

- Threads? Locks? R/W to/from ports only?

- Programming models to abstract the SoC (message passing, SMP, streaming)?

- What do we do with all the legacy code?

- Communication

- Memory sub system design, NoC design