# Programming Models and Software Architecture for MPSoC

### Ahmed A. Jerraya

#### **TIMA Laboratory**

46 Avenue Felix Viallet 38031 Grenoble Cedex France

Tel: +33 476 57 47 59

Fax: +33 476 47 38 14

Email: Ahmed.Jerraya@imag.fr

## Acknowledgement

- Prof F. Pétrot,

- Dr. A. Bouchhima,

- Phd Students

- A. Chureau

- S.I. Han,

- K. Popovici,

- H. Shen

- X. Guerin

- P. Gerin

# Programming Model: The Classical Solution to Abstract HW-SW Interfaces

- Abstract HW model for SW design

- Programming language with implicit primitives (e.g. module hierarchy & threads in SystemC)

- API (MPI, PThreads) & Simulation model (MPICH, Linux)

- Requires an additional SW layer called HW dependent SW (HDS)

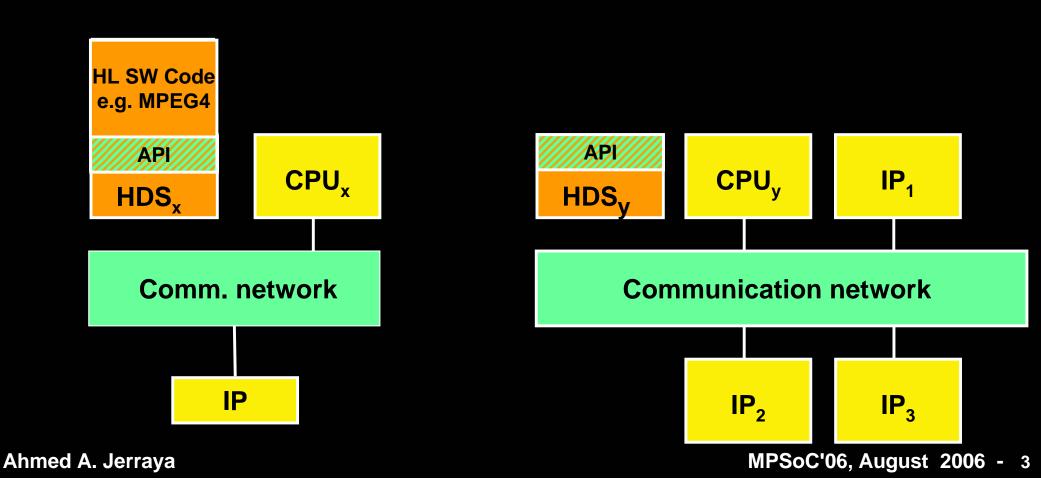

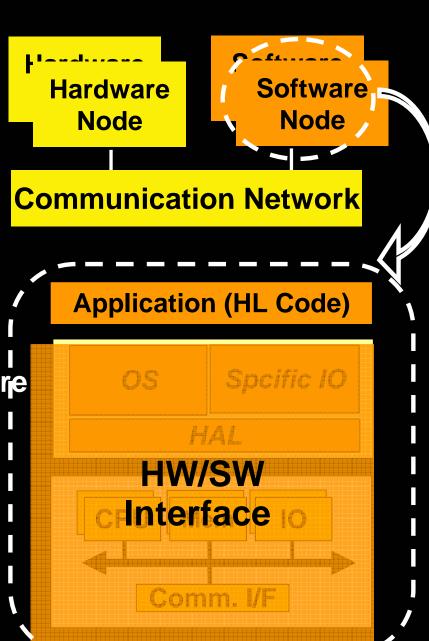

### Context: Heterogeneous MPSoC

- Heterogeneous MPSoC

- software node:

- Specific CPU subsystem

- GPP, DSP, ASIP...

- I/O and Memory architecture

- Layered SW architecture

- High level Application Code

- HDS: Hardware dependent Software

- A Programming Model Abstracts HW-SW interfaces for SoC design

- Specific I/O => specific API

- HDS adapts HL SW to specific HW

- Different abstraction levels

-MPSoC'06, August-2006

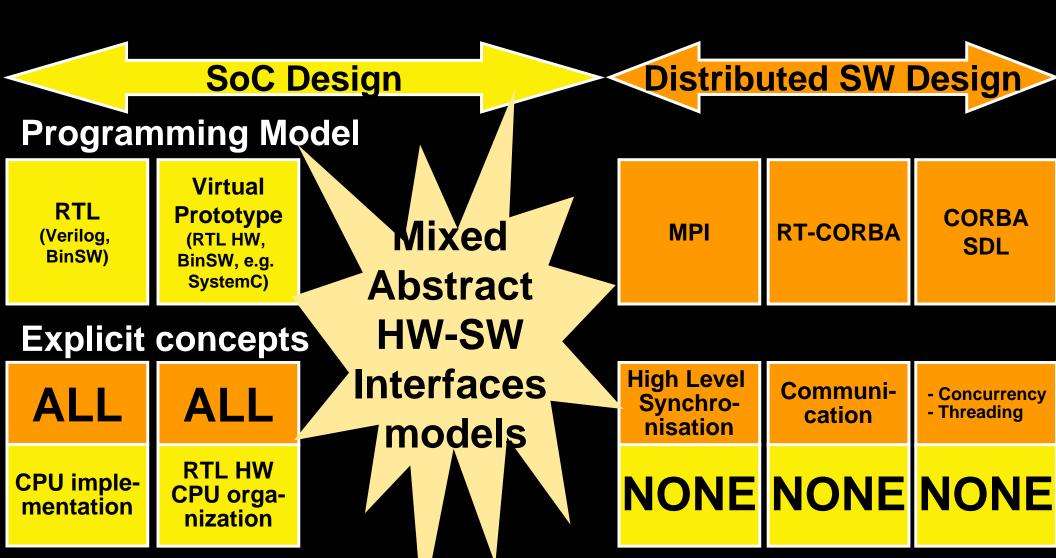

### **Parallel Programming Models:** The mixed HW-SW interfaces GAP

### Parallel Programming Models for MPSoC

### **Distributed SW Design**

#### **Programming Model**

RTL (Verilog, BinSW)

Virtual **Prototype** (RTL HW, BinSW, e.q. SystemC)

Transaction Accurate (TLM HW, TLM SW, e.g. SystemC++)

Virtual **Architecture** (Abstract HW. Threads, e.g. SystemC, Simulink)

**MPI**

**RT-CORBA**

**CORBA** SDL

#### **Explicit concepts**

**ALL**

**CPU imple**mentation

**RTL HW CPU** organization

- OS

- Specific 1/0

-CPU **Subsystem** - Explicit HW modules

Communication/ Computation **Modules**

**Abstract** Interconnect Synchronisation

NONE NONE NONE

Communication

- Concurrency - Threading

- **New HW-SW Abstraction levels**

- **Hiding CPU in addition to HW & SW**

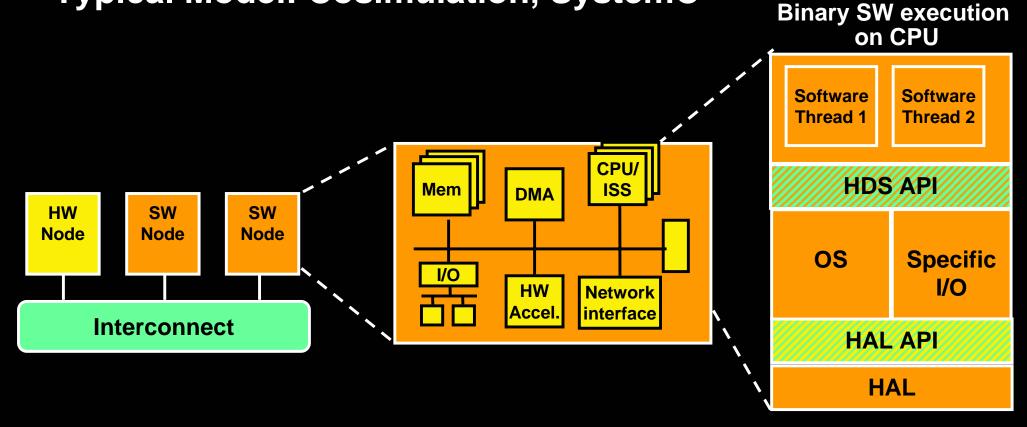

# Programming Models for MPSoC Virtual Prototype

- Explicit SW (Binary)

- Explicit HW

- Implicit CPU Implementation (ISS)

- Cycle accurate Model

- Typical Model: Cosimulation, SystemC

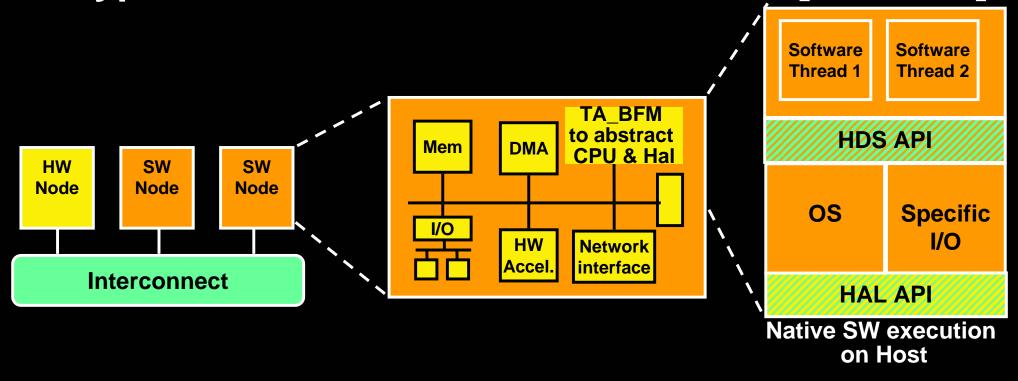

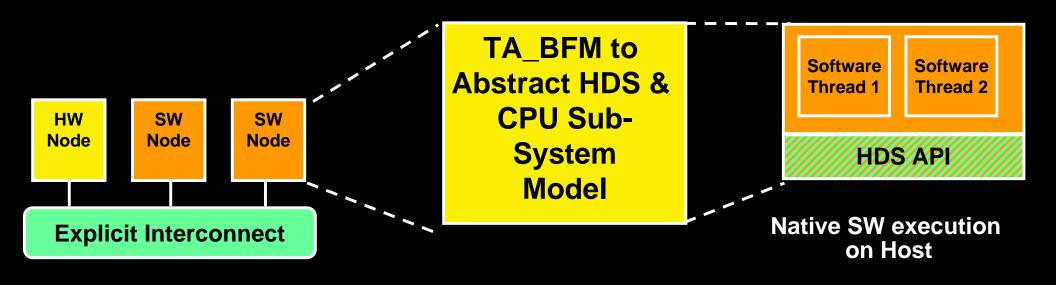

### **Programming Models for MPSoC Transaction Accurate model**

- Explicit OS

- Explicit CPU Subsystem Architecture

- Implicit CPU/HAL (TA\_BFM)

- Transaction cycle accurate HW

- Typical Model: Native SW Execution [ST/TIMA]

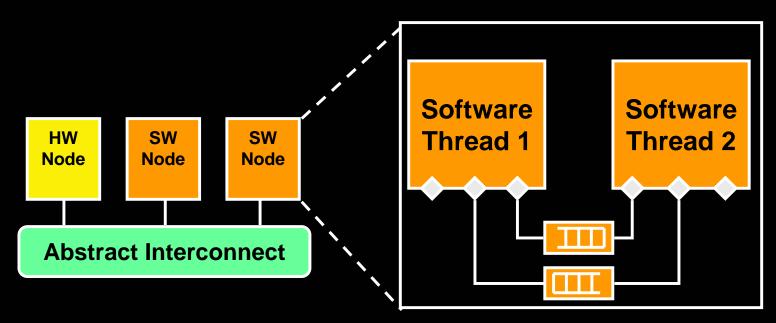

# Programming Models for MPSoC Virtual Architecture model

- Explicit SW communication API

- Explicit System Interconnect

- Implicit HDS (OS, Communication Implementation)

- Typical Models: TTL, DSoC, Pthreads

# Programming Models for MPSoC System Architecture model

- Explicit thread/subsystems & HW-SW partition

- Implicit communication

- Typical Models: MPI, Simulink, KPN

Implicit SW execution as a simulation module

# Conclusions: Programming Models for MPSoC

- Abstract HW-SW Interfaces to enable Higher than RTL design

- Application-specific Implementation allows to reach cost and performances requirements

- Need new design automation techniques

- Is an opportunity for new HW-SW codesign approaches and architecture Exploration

# Thank