## Re-configurable ASIPs:

# Is there any need for these architectures?

28.06.2007, MPSoC 2007, Japan

Heinrich Meyr

### Agenda

- rASIP Application Space

- Future Wireless Communication Systems

- UMIC Many Core Working Assumptions

- rASIP Design Space

- Early rASIP Designs

- Traditional Design Methodology

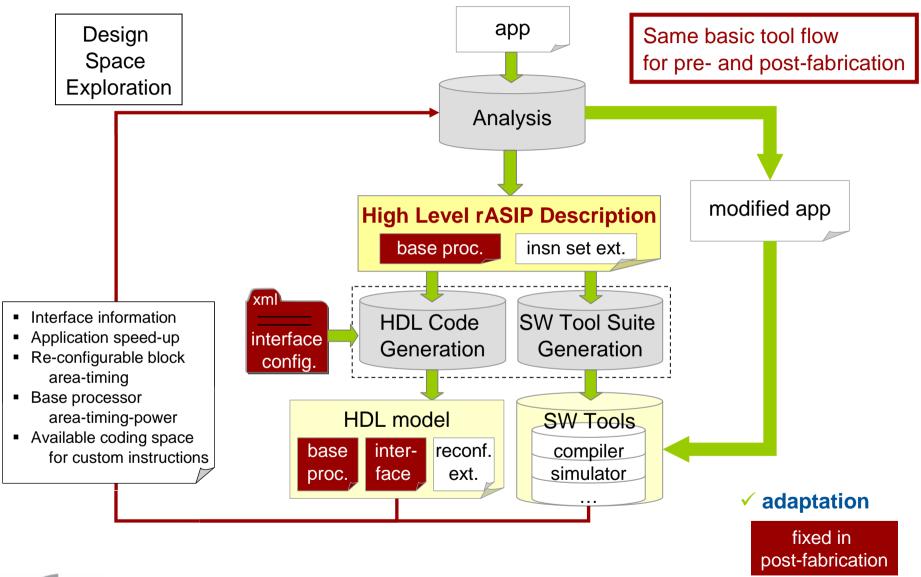

- Proposed rASIP Design Flow

- Pre-Fabrication Design Flow

- Post-Fabrication Design Flow

- Proof of Concept

- Outlook

### Acknowledgement

- The research reported in this talk is based on work of area "RF Subystems and SoC Design" of the "UMIC Cluster" at the RWTH Aachen University

- Principal Investigators

- Prof. T.G. Noll

Institute for Electrical Engineering and Computer Systems

- Profs G. Ascheid / R. Leupers / H. Meyr Chair for Integrated Signal Processing Systems

- Prof. S. HeinenChair of Integrated Analog Circuits

- Prof. P. Mähönen

Ericsson Chair of Wireless Networks

- Prof. S. Kowalewski

Chair for Software for Embedded Systems

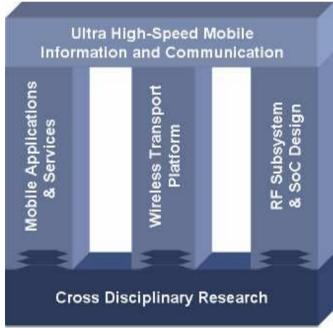

### UMIC Research Cluster at RTWH Aachen

- Ultra high-speed Mobile Information and Communication

- extremely challenging application demands

- limitations of mobile communications and

- technology capabilities and constraints

- The design requires a tremendous leap

- ⇒ needs collaborative research in

- Mobile Applications & Services

- Wireless Transport Platform

- Radio Frequency Subsystems& System-on-Chip (SoC) Design

- Cross Disciplinary Methods & Tools

- Total funding 36mio (2006-2011)

- www.umic.rwth-aachen.de

### Agenda

- rASIP Application Space

- Future Wireless Communication Systems

- UMIC Many Core Working Assumption

- rASIP Design Space

- Early rASIP Designs

- Traditional Design Methodology

- Proposed rASIP Design Flow

- Pre-Fabrication Design Flow

- Post-Fabrication Design Flow

- Proof of Concept

- Outlook

### Future Wireless Systems : Cognitive Radios

- Must sense or be cognitive of the environment

- Other user interference, multipath, noise, etc.

- Time-variations

- Must be intelligent to analyze the situation and find the optimal communications protocol, frequency, channel, etc.

- Must reconfigure for the channel and protocol required

- And...constantly adapt to mobile changing environments

- Will have multiple antennas (MIMO)

- They will make use of ultra-complex and ultra energy efficient signal processing to optimally use the available bandwidth

These radios "find the best protocol, frequency, and channel" to communicate over

### Agenda

- rASIP Application Space

- Future Wireless Communication Systems

- UMIC Many Core Working Assumptions

- rASIP Design Space

- Early rASIP Designs

- Traditional Design Methodology

- Proposed rASIP Design Flow

- Pre-Fabrication Design Flow

- Post-Fabrication Design Flow

- Proof of Concept

- Outlook

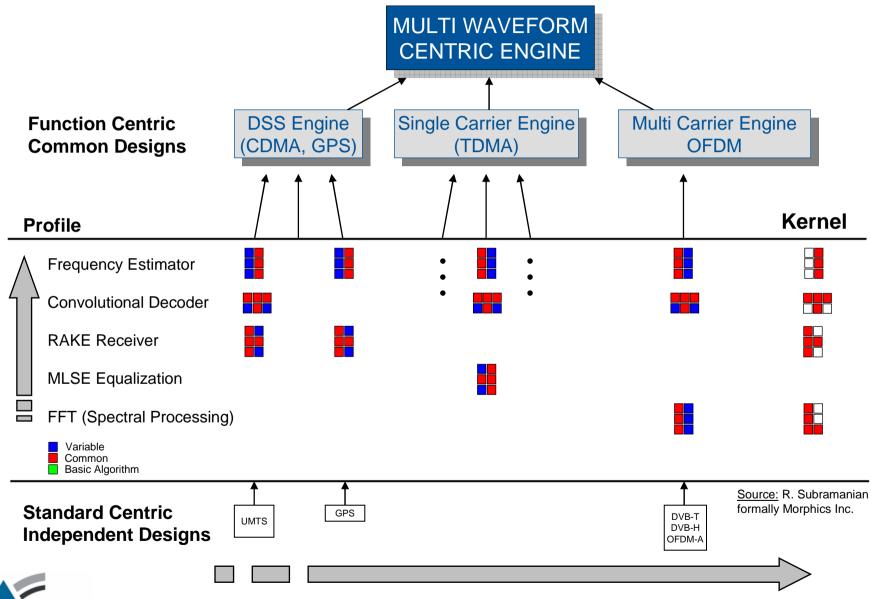

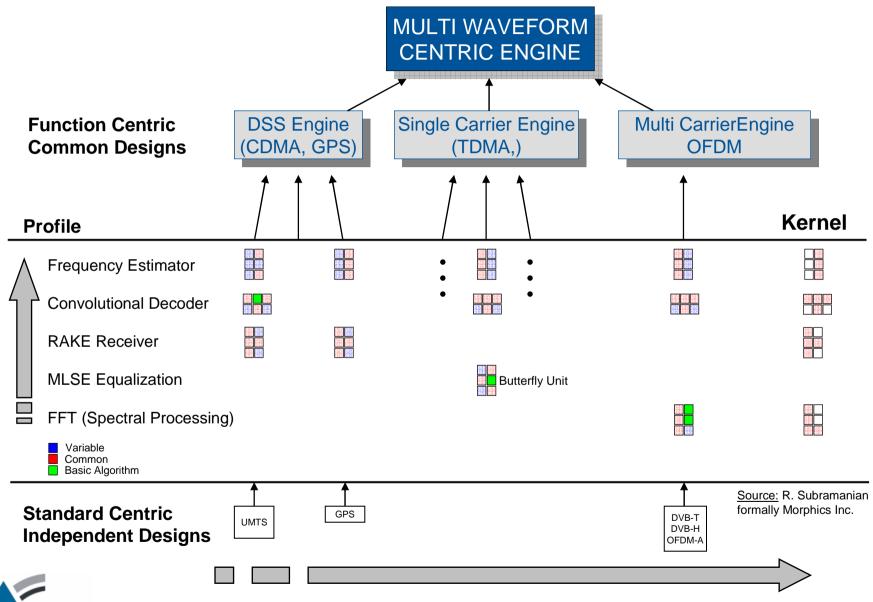

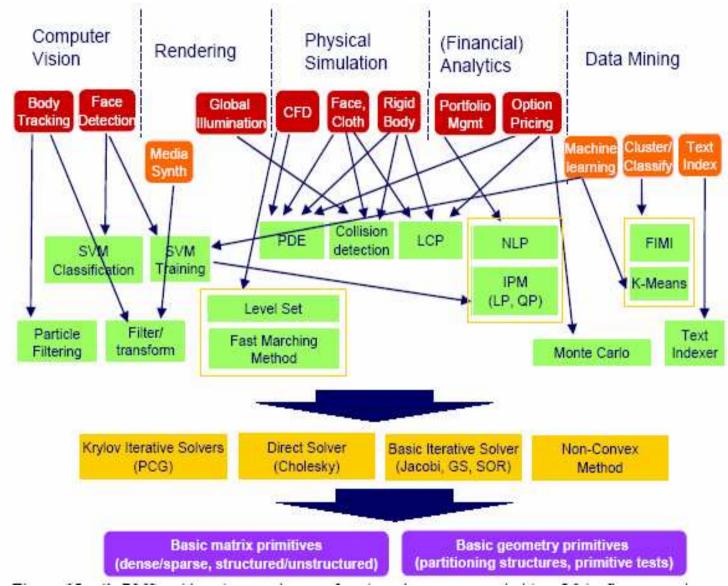

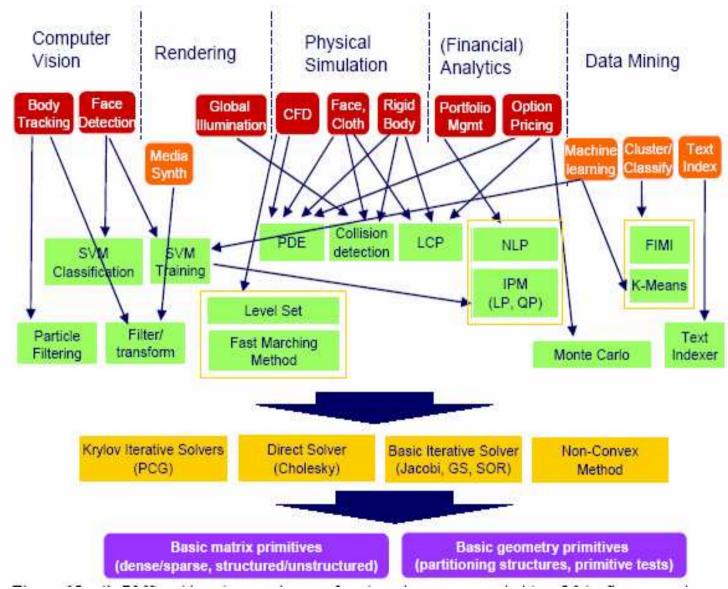

### The "Key Algorithm" Proposition of the UMIC Platform

Each signal processing is based on a small number of fundamental algorithms ("Nuclei") that represent a significant amount of the computation.

⇒ Focus on an efficient composition ("design of an MPSoc) or mapping ("programming of the MPSoC")

#### References:

- UC Berkeley, EECS TR, June 15, 2006

- Ienne, Leupers: Customizable Embedded Processors, August 2006

8

### HW/SW Partitioning: Spatial and Temporal Mapping

### HW/SW Partitioning: Spatial and Temporal Mapping

© H. Meyr

### 1. System Architecture Concept (HW & SW)

### Intel RMS View (Recognition, Mining, Synthesis)

### Agenda

- rASIP Application Space

- Future Wireless Communication Systems

- UMIC Many Core Working Assumptions

- rASIP Design Space

- Early rASIP Designs

- Traditional Design Methodology

- Proposed rASIP Design Flow

- Pre-Fabrication Design Flow

- Post-Fabrication Design Flow

- Proof of Concept

- Outlook

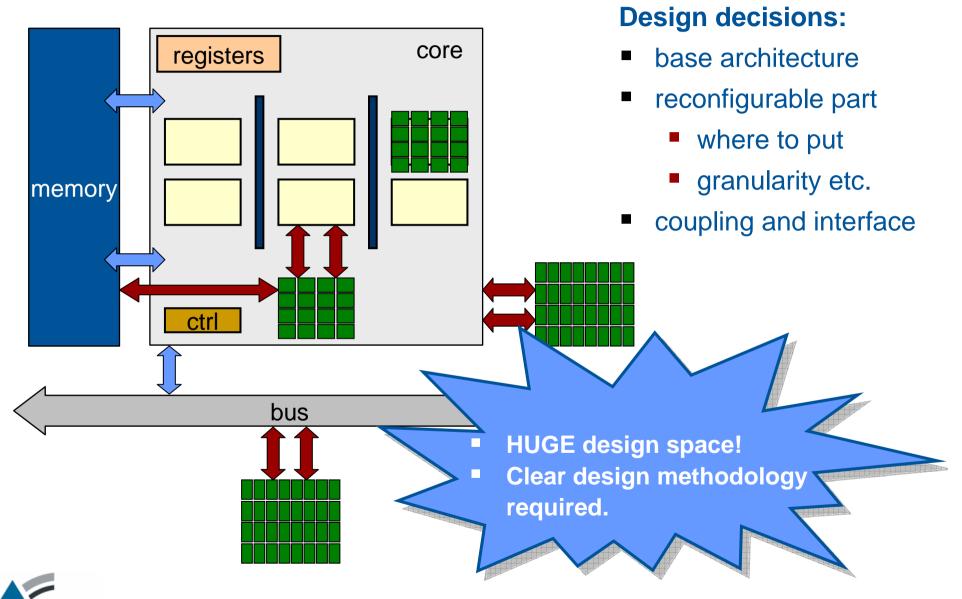

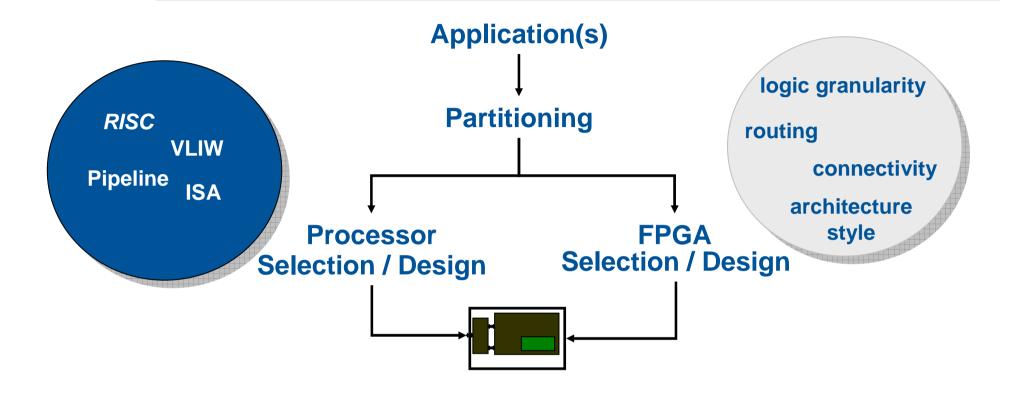

### rASIP Design Space

### Traditional Design Methodology

- Dedicated/ Partially Re-targetable Tools

- Separate Design Space Exploration

- Partial Design Space Exploration

### Agenda

- Reconfigurable systems

- rASIP Application Space

- Future Wireless Communication Systems

- UMIC Many Core Working Assumption

- rASIP Design Space

- Early rASIP Designs

- Traditional Design Methodology

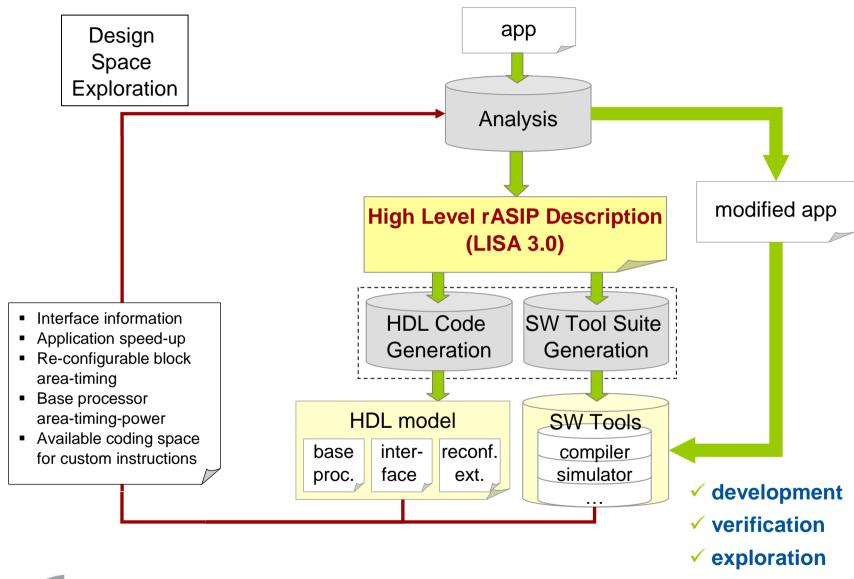

- Proposed rASIP Design Flow

- Pre-Fabrication Design Flow

- Post-Fabrication Design Flow

- Proof of Concept

- Outlook

### **PRE-**Fabrication Phase

### **POST-**Fabrication Phase

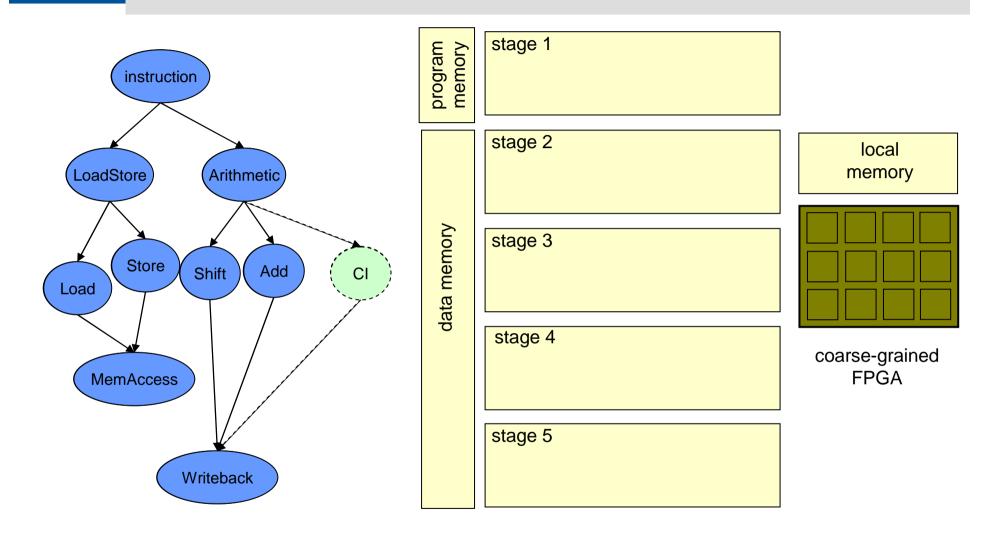

### **Stepwise Processor Modelling**

step 1 : capturing the ISA

step 2: structuring the ISA

### Agenda

- rASIP Application Space

- Future Wireless Communication Systems

- UMIC Many Core Working Assumptions

- rASIP Design Space

- Early rASIP Designs

- Traditional Design Methodology

- Proposed rASIP Design Flow

- Pre-Fabrication Design Flow

- Post-Fabrication Design Flow

- Proof of Concept

- Outlook

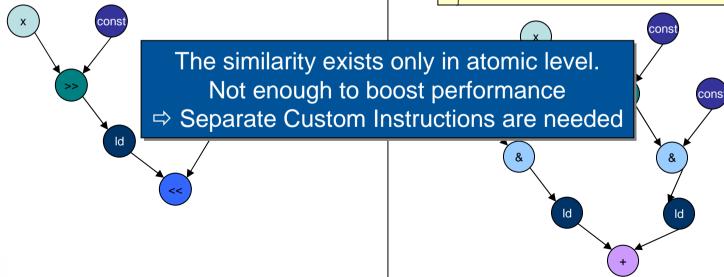

### GOST vs Blowfish Hotspot

### **GOST Hotspot**

### **Blowfish Hotspot**

### **Application Analysis**

### Initial results

- Not good for GOST, better for Blowfish

- Longer operation chains are key to speed-up

### Identifying common characteristics

- Given cryptographic applications access constant S-Boxes from the hot-spots

- Such S-Boxes can be put inside scratch-pads accessible from custom instructions

- Conclusion: Scratch-pad access from custom instructions might result in higher speed-ups

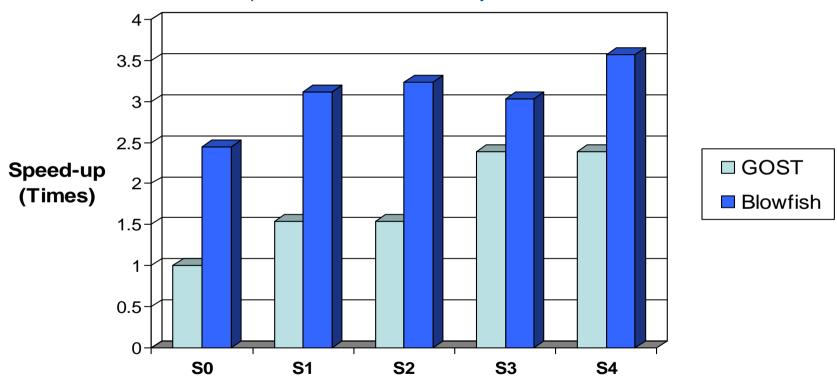

### **Design Space Exploration Results**

■ GOST: 105 data points

■ Blowfish: 120 data points

- Custom Instruction Synthesis with various latencies, area constraints

- From 0 to 4 scratch-pad access per custom instruction

- Total exploration time: 2 man days

Custom instructions Set synthesis tool: R.Leupers, K.Karuri, RWTH Aachen)

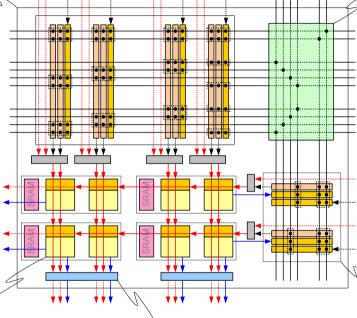

### Overview: Architecture and Parameters

#### Cluster

- horizontal LEs per row C<sub>H</sub>=[1..64]

- vertical LEs per column C<sub>V</sub>=[1..64]

- global inputs north I<sub>N</sub>=[0.4]

- global inputs west l<sub>W</sub>=[0..4]

- global inputs south I<sub>S</sub>=[0..4]

- global inputs east I<sub>E</sub>=[0..4]

- output directions

- D<sub>CL</sub>=any set from [north,west,south,east]

- output ports (LE-ports)

- granularity M<sub>CL</sub>=[1..C<sub>H</sub>] (only adjacent LEs in a row)

same for all clusters

#### general

- horizontal clusters in eFPGA S<sub>H</sub>=[1..256]

- vertical clusters in eFPGA S<sub>V</sub>=[1..256]

#### **Routing Switch**

- horizontal tracks W<sub>H</sub>=[1..256]

- vertical tracks W<sub>V</sub>=[1, 256]

- switch-positions as index of crossing vert. and hor. lines P<sub>RS,i</sub>=[i<sub>V,i+</sub>] (only F<sub>S</sub>=3, no cascaded SPs)

- SP-definition SP<sub>i</sub>=set of routes

- per track i: segment length Li=[1..256]

- granularity M<sub>RS</sub>=[1..64] (only adjacent switch points)

same for all RS

#### Logic Element

Dedicated Routing Block (DRB)

inputs from other LEs and broadcast defined per input of Core Logic [list]

Core Logic (CL) only for configurator

set of functions with according CL-in-/ outputs (from DRB and dedicated) [list]

same for all LEs

#### Register-Stage

only for configurator

- LEs in a column per register N<sub>Reg</sub>=[1..C<sub>V</sub>]

- register-chain RC=[yes,no]

- LE-outputs with register [list]

- broadcast lines with register [list]

same for all register stages

#### **Connection Box**

- switch positions per cluster in-/output: set of tracks described by track index i<sub>track</sub>, LE-index i<sub>LE</sub> (row or column) and ranges of tracks r<sub>track</sub>

- $P_{CP,i}=f(i_{track},r_{track},i_{LE})$

- granularity M<sub>CB</sub>=[1..64] (only adjacent connection points)

same for all CBs and defined only once per cluster-row (-column)

Source: T.G. Noll, RWTH Aachen

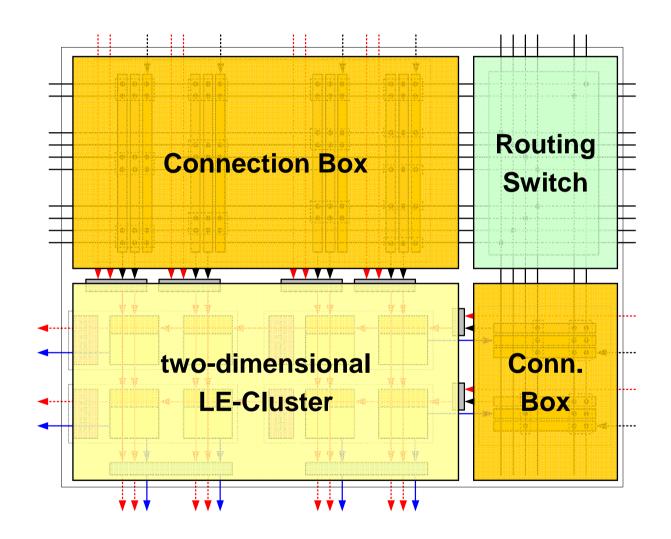

### Parameterisable FPGA Architecture – Template

### Parameterisable FPGA Architecture – Template

### Cluster

# LEs (horiz. / vert.)

# Broadcast lines

# shared SRAMs

I/O directions

### Logic element

Functionality (Core logic)

Connectivity (DRB)

### Register stage

# LEs (Column) per Reg.

# LE-outputs with Reg.

Type (Register, Latch, ...)

### **Routing Switch**

# lines

Switch-positions

Connectivity per Switch Point

Segment lengths

# shared SRAMs

### **Connection Box**

# Lines per group

Window width

Phase position of window

Window periodicity

# shared SRAMs

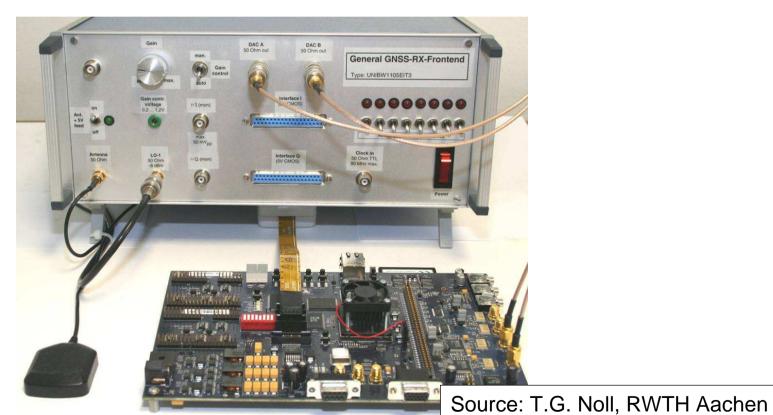

### **GNSS** Prototype Hardware

- Multioperable GNSS frontend

- Supports: NavStar GPS, Glonass, Galileo, Egnos, ...

- 1575 1620 MHz

- Flexible FPGA based receiver

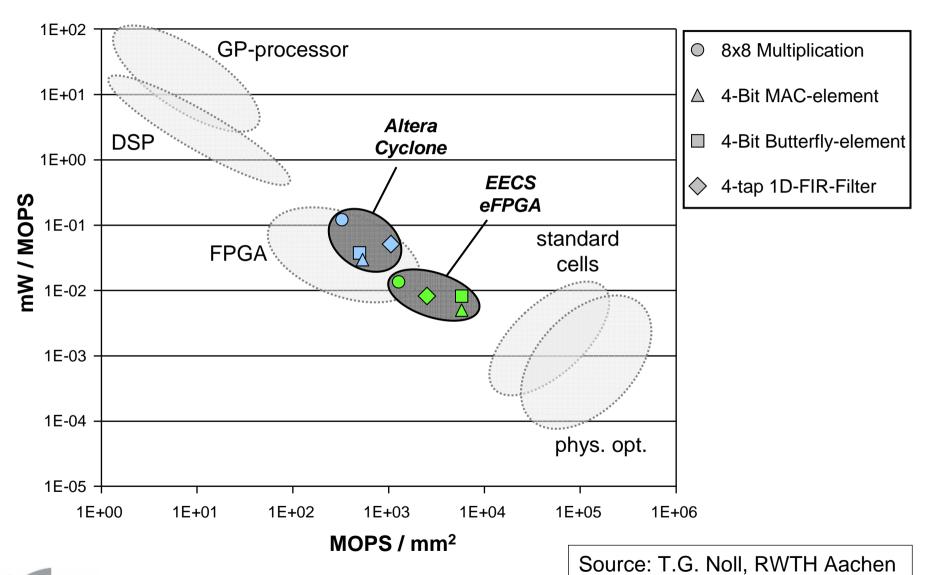

### Arithmetic oriented eFPGA vs. commercial FPGA

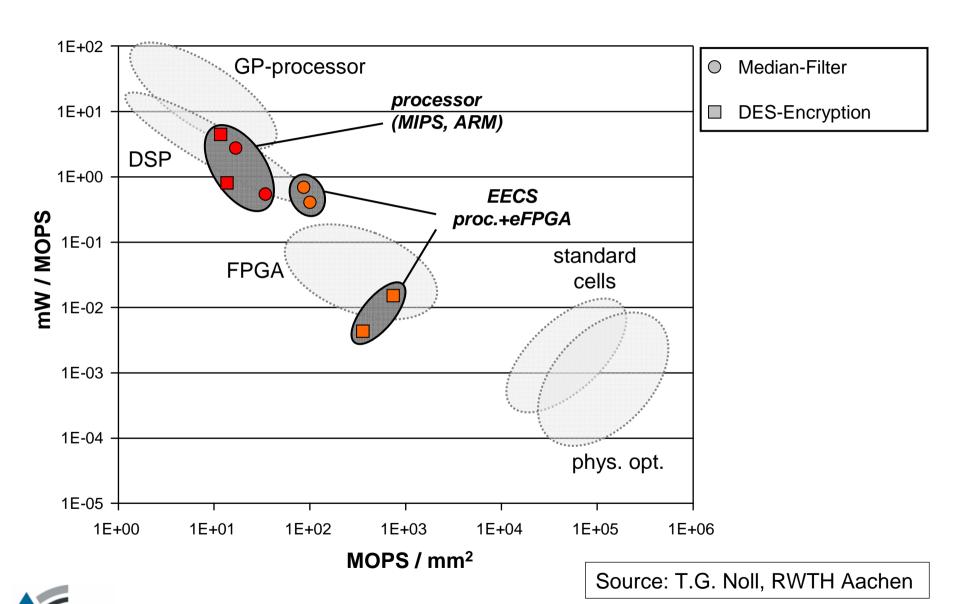

### Reconfigurable Processor vs. Standard Processor

29

### Agenda

- Reconfigurable systems

- rASIP Application Space

- Future Wireless Communication Systems

- UMIC Many Core Working Assumption

- rASIP Design Space

- Early rASIP Designs

- Traditional Design Methodology

- Proposed rASIP Design Flow

- Pre-Fabrication Design Flow

- Post-Fabrication Design Flow

- Proof of Concept

- Outlook

### Conclusion

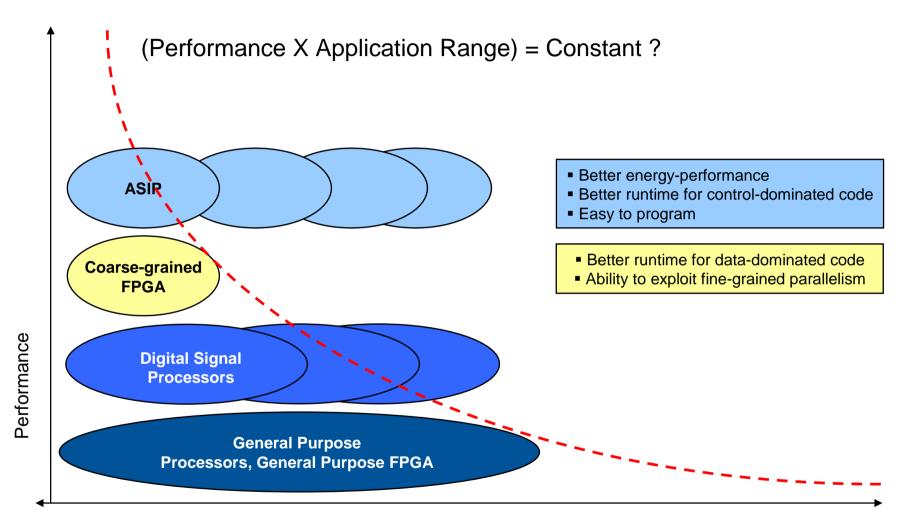

- rASIPs allow combining the benefits of both ASIP and FPGA

- In view of future wireless applications, this is desired

- Embedded domain-specific eFPGA macros are key for high area/energy efficiency

- Pre-fabrication design-space exploration is absolutely essential

- Post-fabrication tools for programmability and reconfigurability are absolutely essential

- Language-driven (LISA 3.0) rASIP tool suite is proposed

### Outlook

### Processor Design flow with Embedded FPGAs

- Current research

- Generic Modelling, Exploration and Implementation of embedded FPGAs

- Integration of rASIPs into complete SoC design flow (virtual prototyping)

### Applying the Methodology

Cognitive radio, an upcoming research challenge for system designers, will be handled with the proposed tools and methodology

# **Thank You**

### Intel RMS View (Recognition, Mining, Synthesis)

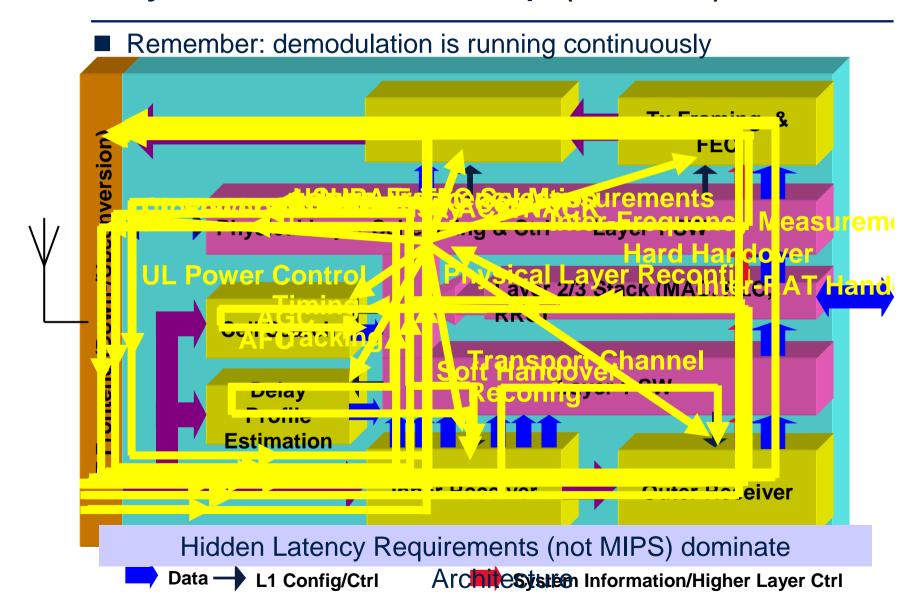

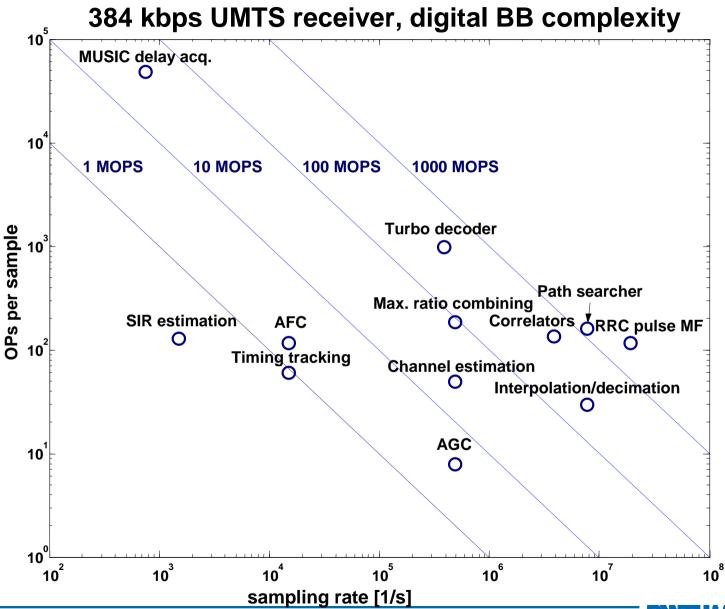

### 384 kbps UMTS Receiver BB Complexity

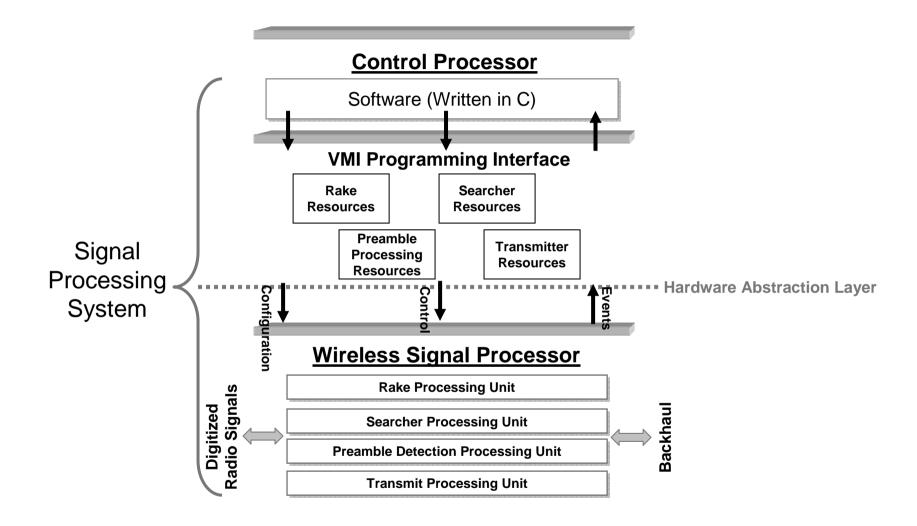

### **SW Programming Model**

### On Flexibility

**Evolving / Changing Applications**