# MPSoC2015

# How to Develop 4K Realtime HEVC Encoder by FPGA

Yuichi Nakamura, NEC Corp.

High Efficiency Video Coding (HEVC) is proposed

It achieves 2x compression ratio than current video codec H.264/AVC.

4K/8K video transmission using HEVC is expected

Hardware real-time encoder is necessary for broadcasting

**HEVC Encoder**

HEVC algorithm introduces variety of complicated coding options

- E.g. various block sizes and predictions

- Encoders should explore optimal one and use it.

Various predictions

NEC

Empowered by Innovation

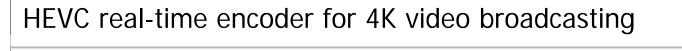

Various Block Sizes

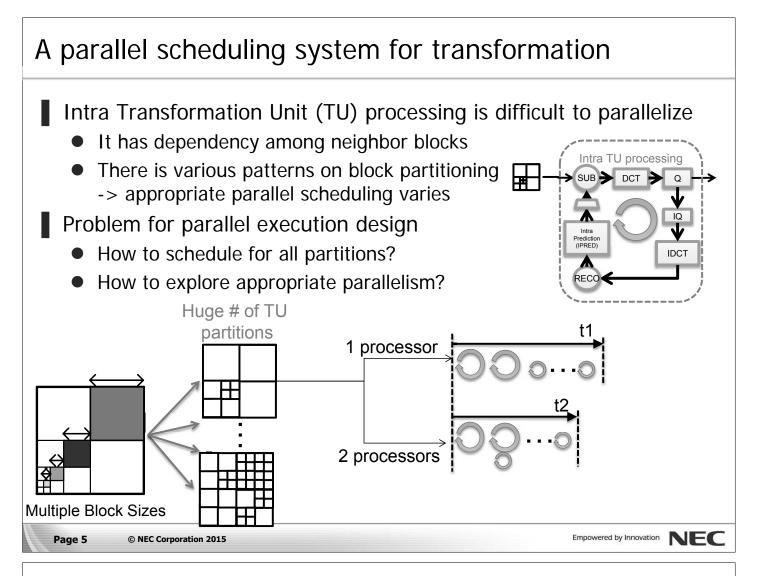

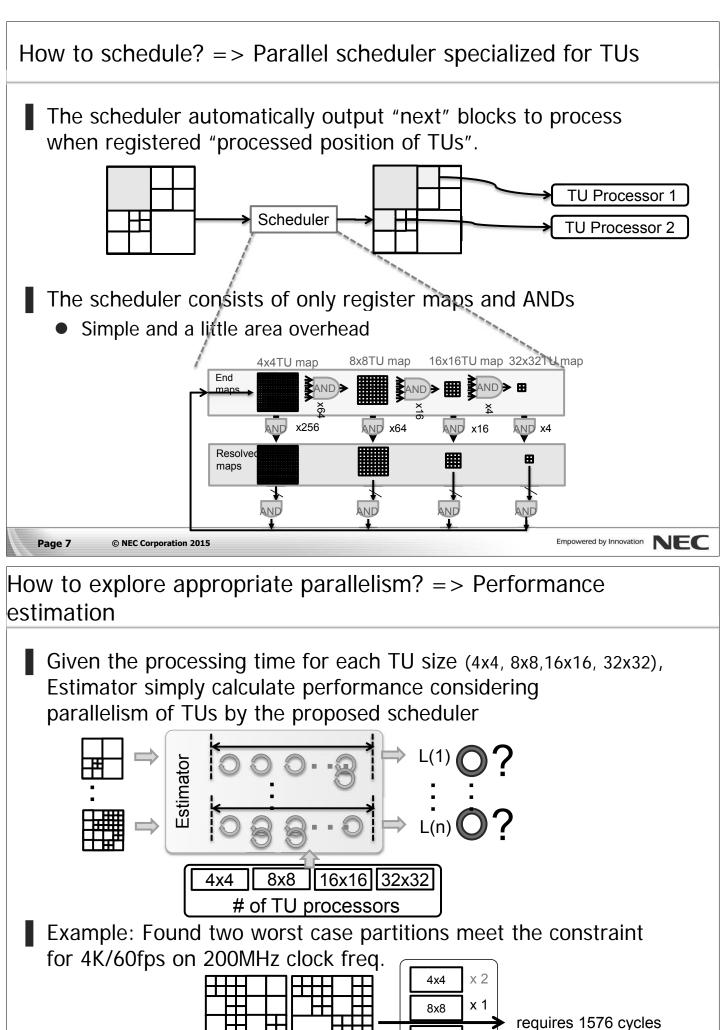

#### Adoption of FPGA: pros. and cons. O FPGA as a product can reduce Time-to-Market No manufacturing time after design phase Designers can verify the system using real input videos. The only solution in order to release product just 1 year after HEVC specification is approved. Manufacture Design Test × The clock frequency of FPGA is relatively low At most 200MHz -> a few cycles per pixel block Parallelism design is important. × It is difficult to implement huge multiplexers. Increase of multiplexers HEVC's various options often introduce huge multiplexers to select various inputs and outputs Empowered by Innovation NEC Page 3 © NEC Corporation 2015 2 technologies to realize HEVC encoder on FPGA A parallel scheduling system for transformation Technology to overcome low frequency by parallelization Introduces parallelizing scheduler and

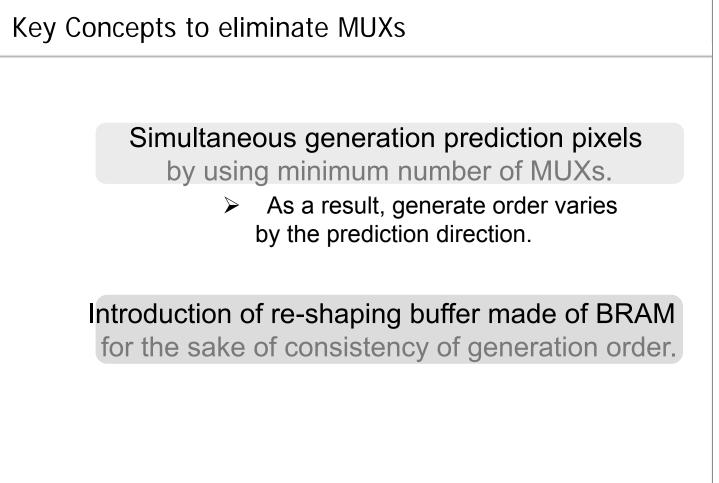

An intra prediction image generator method

• Technology to reduce huge multiplexers

# Difficulty comparison of H.264/AVC and H.265/HEVC

| Parallelism is behind complicated TU partitions and dependencies |                                                    |                                                                 |  |  |  |

|------------------------------------------------------------------|----------------------------------------------------|-----------------------------------------------------------------|--|--|--|

|                                                                  | H.264/AVC                                          | H.265/HEVC                                                      |  |  |  |

| TU<br>dependency                                                 | Low                                                | High                                                            |  |  |  |

| TU size                                                          | 2 sizes                                            | 4 sizes <sup>8</sup> 32                                         |  |  |  |

| TU partition patterns                                            | Uniform partition of<br>16x16<br>(only 2 patterns) | Non-uniform<br>partition of 64x64<br>( > 1 million<br>patterns) |  |  |  |

| Parallelism                                                      | Obvious                                            | Depends on the<br>TU partitions<br>determined on-line.          |  |  |  |

|                                                                  |                                                    | determined on-line.                                             |  |  |  |

< 1646 (4K 60fps)

© NEC Corporation 2015

Page 8

x 1

x 1

16x16

32x32

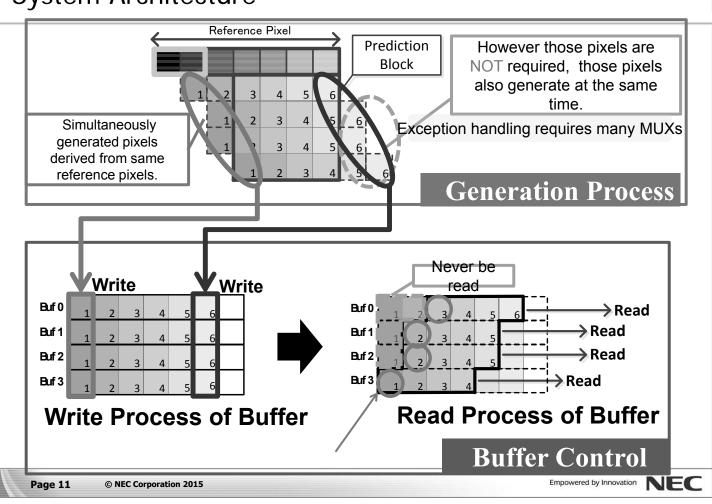

#### An intra prediction image generator method

In HEVC, # of intra prediction direction is 33 (from 9 in H.264/AVC)

For block sizes from 4x4 to 32x32

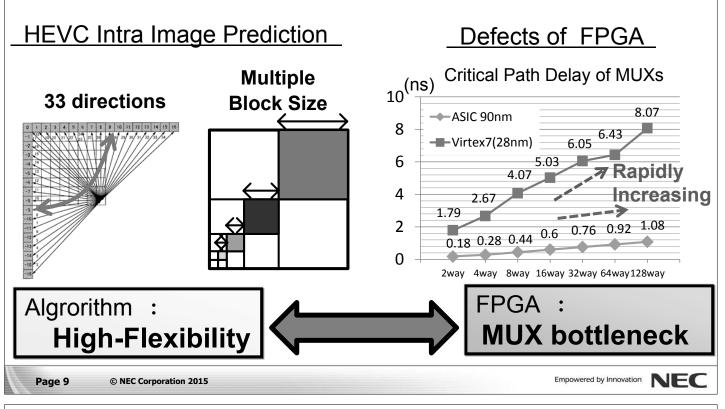

### System Architecture

#### **Evaluation Results**

#### Resource Usage

|                    | Raster scan architecture | Proposed | Ratio             |

|--------------------|--------------------------|----------|-------------------|

| Slice LUTs         | 3693                     | 1910     | -51%              |

| Slice<br>Registers | 1211                     | 2508     | 100% <sup>†</sup> |

| F7 MUX             | 329                      | 97       | -71%              |

| F8 MUX             | 96                       | 48       | -50%              |

| BRAM               | 0                        | 16       | N/A               |

| DSP48              | 64                       | 64       | 0%                |

#### Maximum Frequency (MHz)

|            | Raster scan<br>architecture | Proposed | Ratio |

|------------|-----------------------------|----------|-------|

| Maximum    | 1012                        | 149.2    | 120/  |

| Frequency. | 104.3                       | 149.2    | 4370  |

#### Summary

# **Orchestrating** a brighter world

NEC brings together and integrates technology and expertise to create the ICT-enabled society of tomorrow.

We collaborate closely with partners and customers around the world, orchestrating each project to ensure all its parts are fine-tuned to local needs.

Every day, our innovative solutions for society contribute to greater safety, security, efficiency and equality, and enable people to live brighter lives.

# Empowered by Innovation