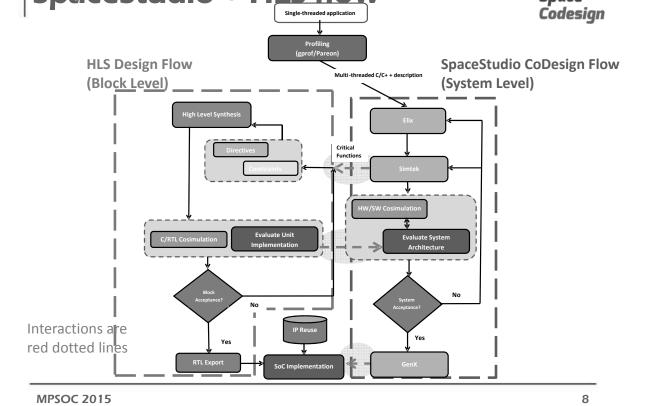

- System Level Exploration and Synthesis

- SpaceStudio + Vivado HLS

- HW/SW Refinement

- Example

| Why HLS <sup>1</sup>                                                                                                                                                                                       | Space<br>Codesign |  |                                                            |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|--|------------------------------------------------------------|

| HLS is a viable alternative to HW designs<br>using HDL                                                                                                                                                     | jn                |  |                                                            |

| <ul> <li>HLS produces better results than previous<br/>tools</li> </ul>                                                                                                                                    |                   |  |                                                            |

| Time to market Rapid exploration of HW solution space                                                                                                                                                      |                   |  |                                                            |

|                                                                                                                                                                                                            |                   |  | FPGAs have become large enough to justi<br>the need of HLS |

| Easier modifiability/maintainability                                                                                                                                                                       |                   |  |                                                            |

| 1. J. H. Anderson, Keynote at AHS 2015                                                                                                                                                                     |                   |  |                                                            |

|                                                                                                                                                                                                            |                   |  |                                                            |

| Limitation of HLS (1)                                                                                                                                                                                      | Space             |  |                                                            |

|                                                                                                                                                                                                            | Codesign          |  |                                                            |

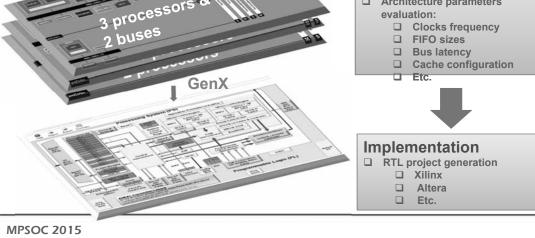

| What about the SW interface (Firmware)?                                                                                                                                                                    | Codesign          |  |                                                            |

| <ul> <li>What about the SW interface (Firmware)?</li> <li>One must be able to:</li> </ul>                                                                                                                  | Codesign          |  |                                                            |

| What about the SW interface (Firmware)?                                                                                                                                                                    | Codesign          |  |                                                            |

| <ul> <li>What about the SW interface (Firmware)?</li> <li>One must be able to: <ul> <li>Profile the application</li> <li>Alter SW binary to call HW accelerators (e.g. (</li> </ul> </li> </ul>            | Ćodesign          |  |                                                            |

| <ul> <li>What about the SW interface (Firmware)?</li> <li>One must be able to: <ul> <li>Profile the application</li> <li>Alter SW binary to call HW accelerators (e.g. (functions))</li> </ul> </li> </ul> | Ćodesign          |  |                                                            |

**MPSOC 2015**

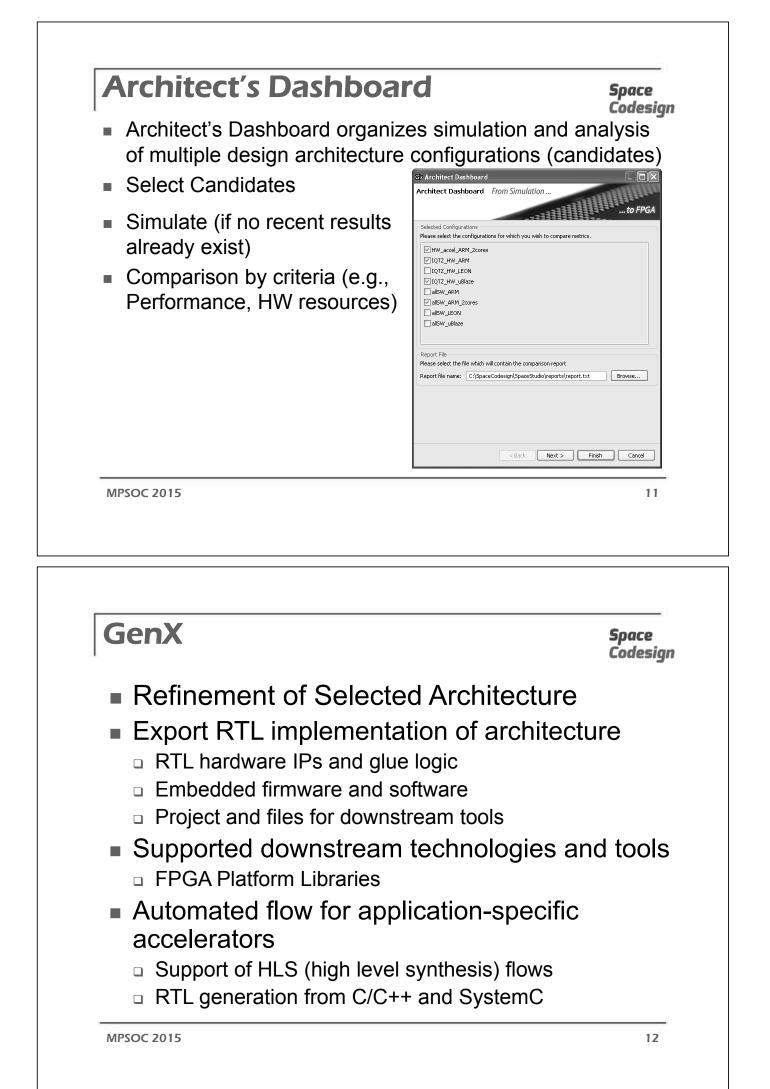

| Software Generation                   | <b>Space</b><br>Codesign          |

|---------------------------------------|-----------------------------------|

| Generated for each processor co       | ore                               |

| Embedded software                     |                                   |

| SW-mapped modules as RTOS tas         | ks                                |

| Communication drivers (kernel driver) | ers)                              |

| Board support package (BSP)           |                                   |

| RTOS configuration files              |                                   |

| OS-specific (e.g., Embedded Linux     | <ul> <li>device trees)</li> </ul> |

| Build files                           |                                   |

| May also generate boot logic          |                                   |

| Bootloader, boot ROM, etc.            |                                   |

| MPSOC 2015                            | 13                                |

## Examples

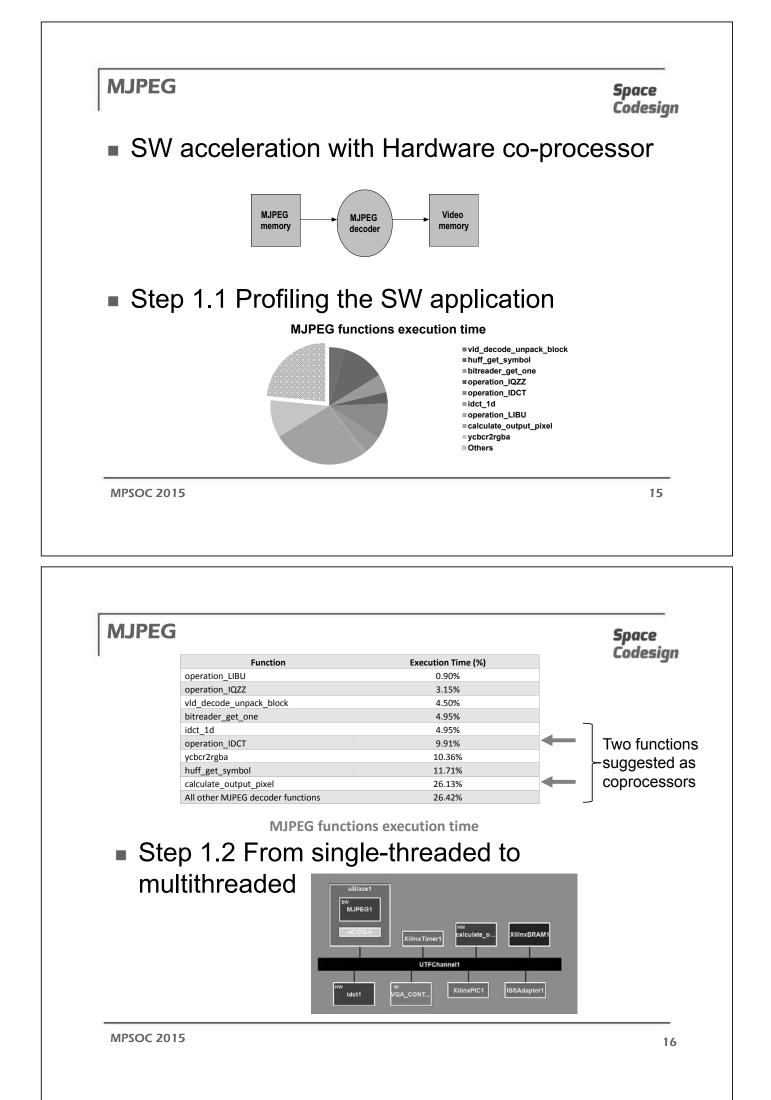

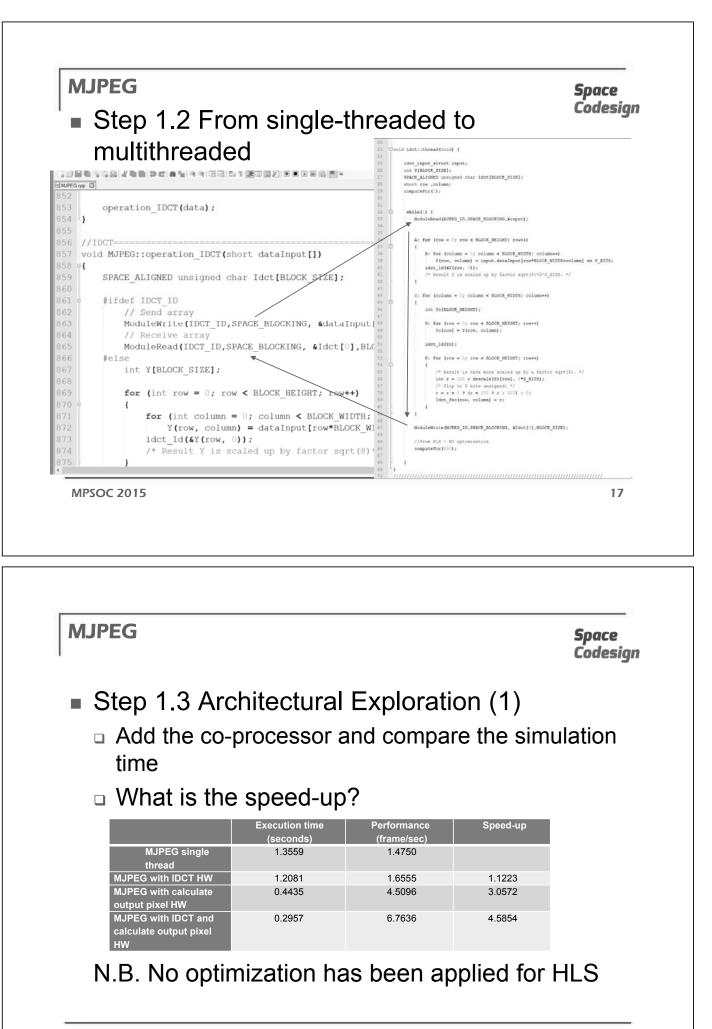

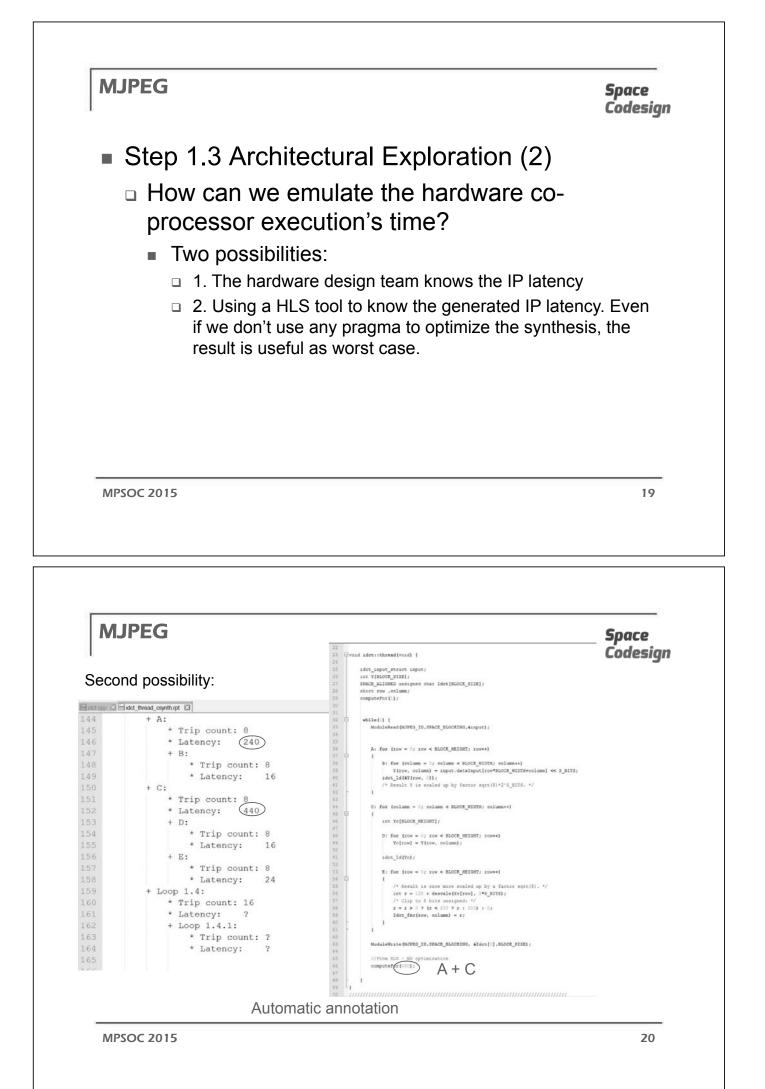

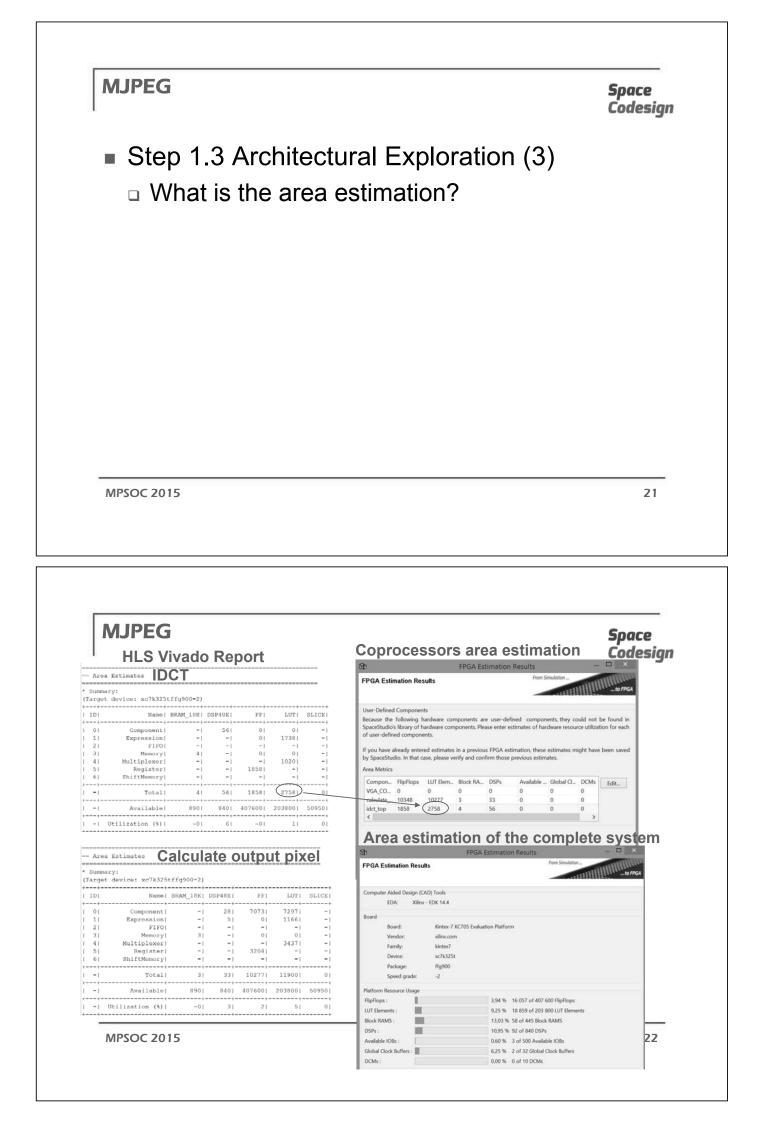

- MJPEG SW acceleration with Hardware coprocessor

- Sobel Filter:

- See <u>http://youtu.be/OKp\_3jitxZM</u>

**Space** Codesign

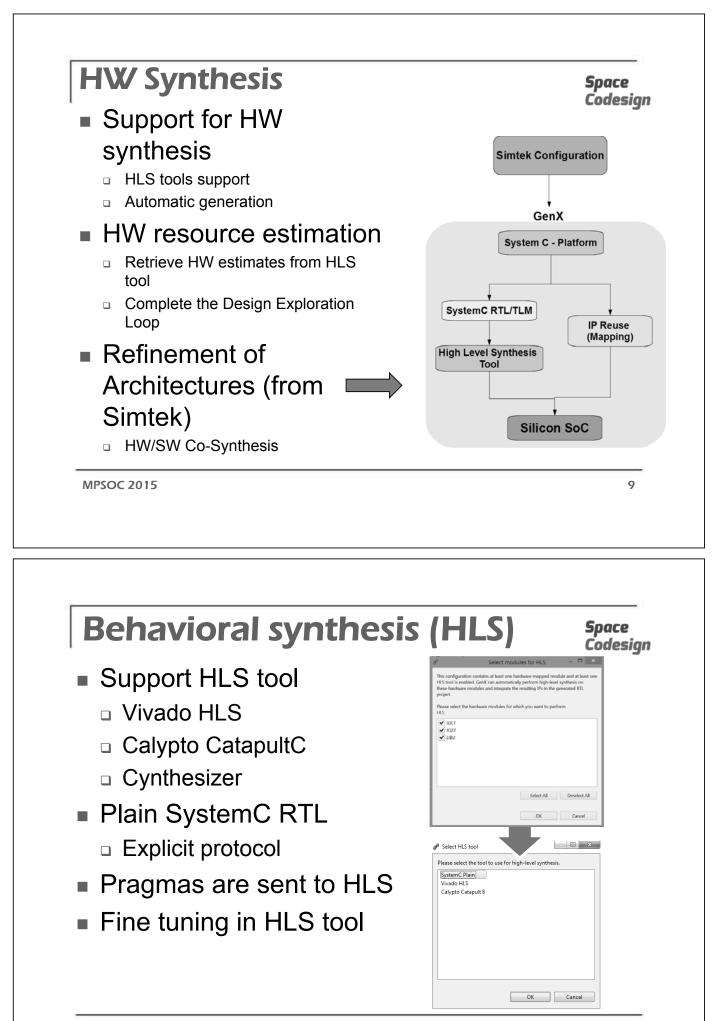

| MJF  |                                                                                                                                                                                                                                                                                             | Space<br>Codesign |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|

|      | Step 1.3 Architectural Exploration (4)<br>Other questions that can be answerd in minute<br>(rather than hours/days):                                                                                                                                                                        | es                |

| 1.   | What would be the effect on the frame rate if we replace the uBlaze by a Cortex A9?                                                                                                                                                                                                         |                   |

| 2.   | The parameter "read/write miss penalty" is currently set at 3 cycles for cache L1 and 2 for cache L2. What will be the effect on the frame rate if this parameter is divided by 3 cache L1 (1 cycle) and by 4 for cache L2 (5 cycles)? <i>(Keep modifications of previous requirements)</i> | •                 |

| 3.   | The current size of all FIFOs used for communication is 64, but we must save hardwar resources. What will be the impact on the performance if we decrease the size of all F 16? (Keep modifications of previous requirements)                                                               |                   |

| Et   | С.                                                                                                                                                                                                                                                                                          |                   |

| MPSO | C 2015                                                                                                                                                                                                                                                                                      | 23                |