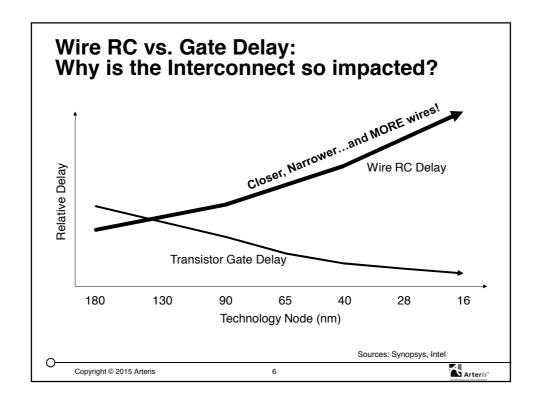

## Physical Interconnect IP Challenges <28nm

Interconnect is more & more difficult to implement

@ 28nm & below

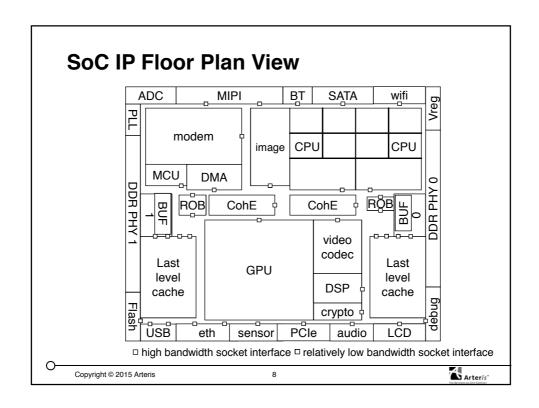

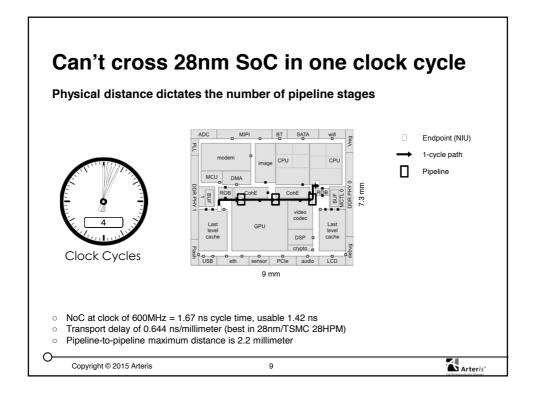

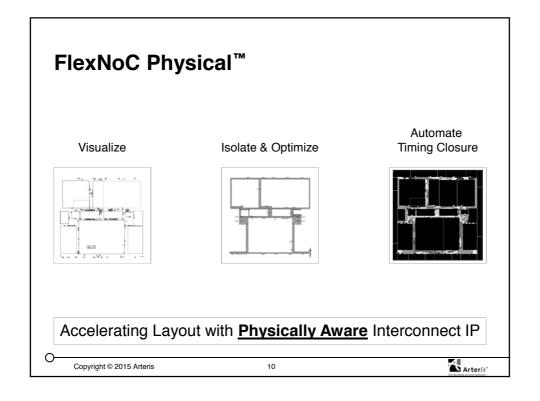

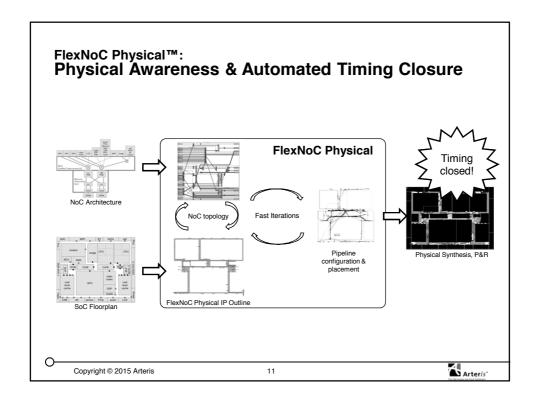

- o Architects need to visualize physical impact of their SoC topologies

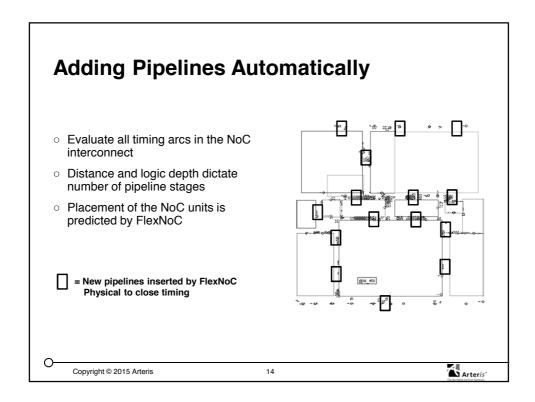

- o RTL engineers can spend months adding pipelines manually

- · Start again with major interconnect changes such as derivatives

- · Overdesign area & timing slack, raising SoC cost & power

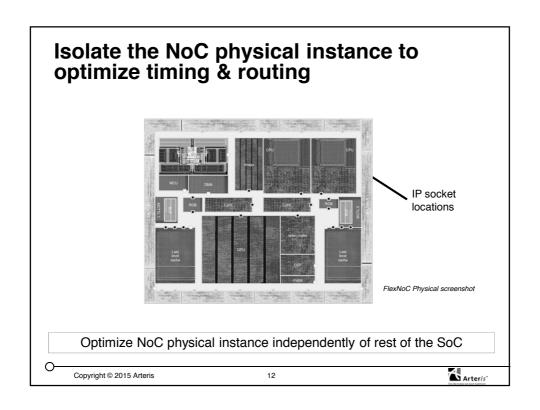

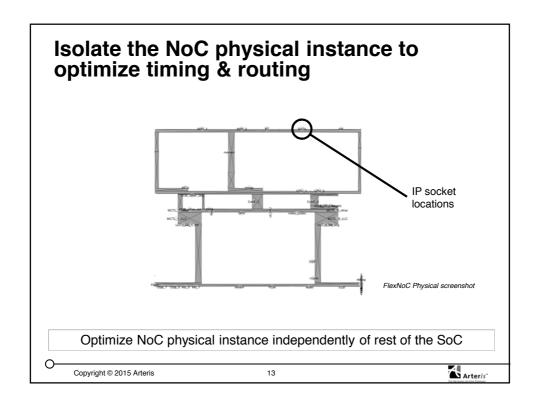

- o Layout engineers given interconnect IP RTL not physically verified

- Have little idea what the architect intended from physical perspective

- · Have to overcome routing congestion and timing closure problems

- · Timing is not closed at the RTL level, creating multiple P&R loops

Copyright © 2015 Arteris

Arteris

## FlexNoC Physical Benefits

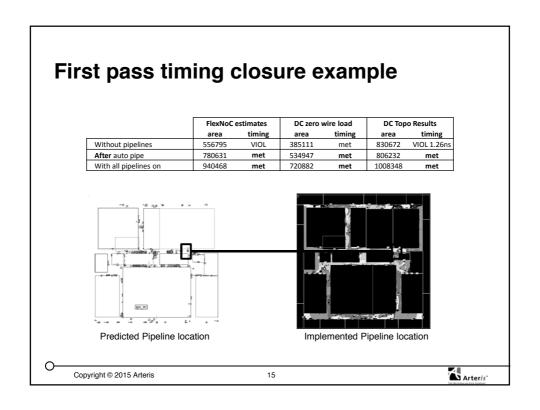

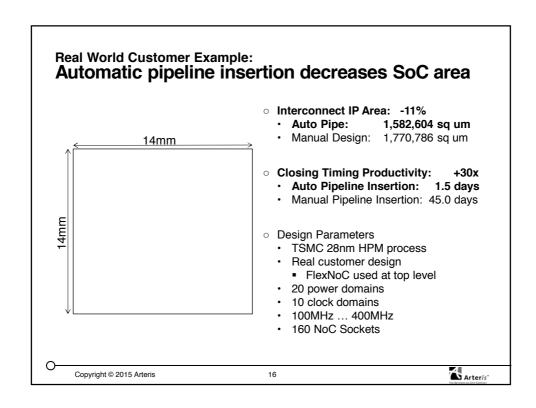

1. Save 1-3 months of iterations with automatic pipeline insertion

- 2. Save 5-15% of interconnect area vs. having to overdesign with excessive number of pipelines

- **3. Improve performance** by matching timing goals to implementation of each NoC IP version vs. overdesign

- **4. Provide a better starting point** for layout process to cut place & route cycles and improve layout productivity

Copyright © 2015 Arteris

17