# **3D MULTICORE: FROM WIDEIO TO PHOTONIC INTERPOSERS**

MPSOC | CLERMIDY Fabien | July 11, 2016

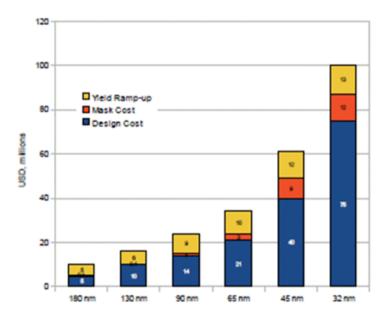

- SoC development cost is exponentially increasing

- Limited to huge mass markets?

- But

- Power efficiency, new applications, big data, fragmented market of IoT...

- New design solutions?

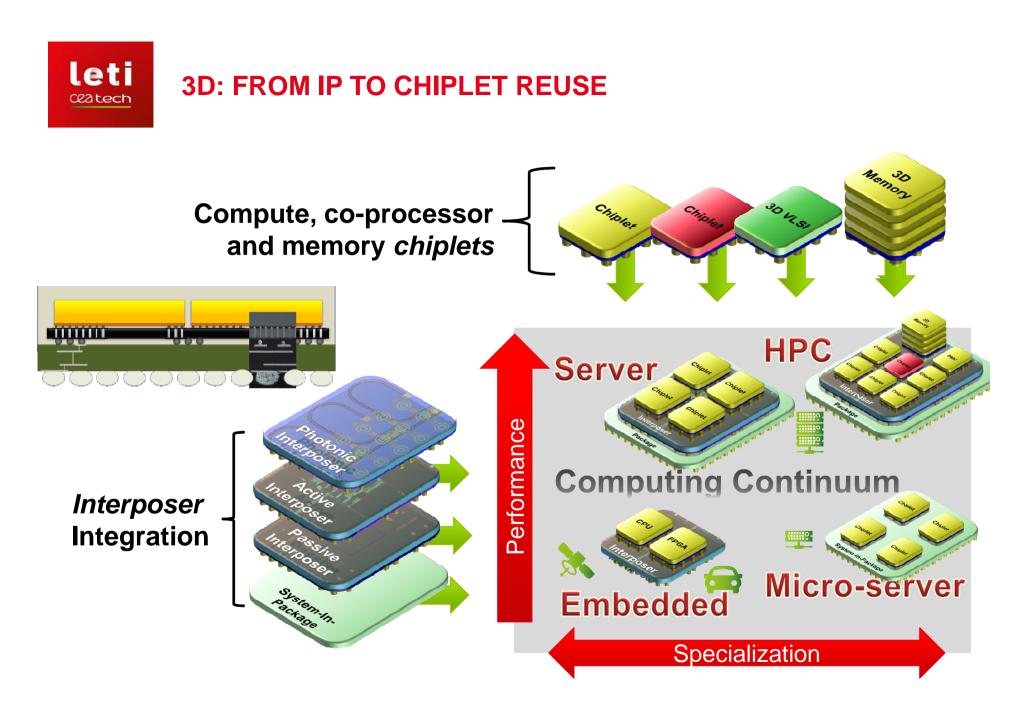

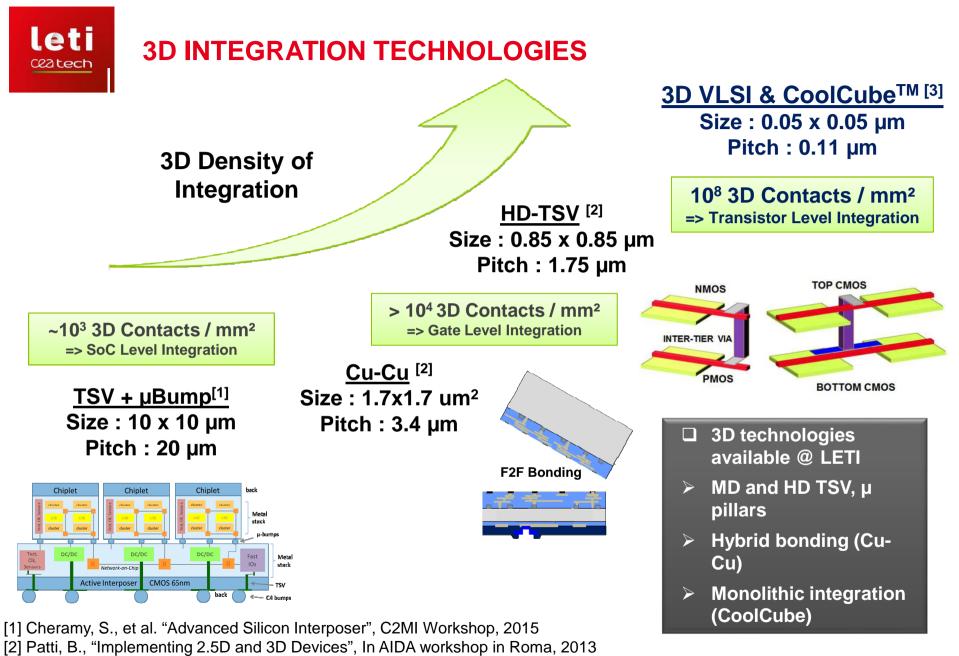

- 3D technologies are now mature

- After 2D scaling, going 3D is a natural extension

- 3D is multiform and can provide a full range of possibilities:

- Advanced packaging

- Yield improvement

- Performance (power/frequency) increase

- Heterogeneous integration

- Scalability and modularity

[3] Batude, P., et al. "3DVLSI with CoolCube process: An alternative path to scaling ." VLSI technology symposium

MPSOC | CLERMIDY Fabien | July 11, 2016 | 5

# leti 3DNOC:

# **3DNOC: A LOGIC-ON-LOGIC MULTI-CORE**

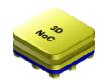

# • 3D Network-on-Chip based multi-core

- Heterogeneous multi-core, MIMO 4G-Telecom application

- Stack 2 similar dies on top of each others

- No global clock, robust asynchronous 3D links

- Serial link for throughput / #TSV trade-off

- 3D-DFT & Fault Tolerance Scheme

| n | kop DHa<br>3DNOC<br>Bottom Da                   |                                     |  |

|---|-------------------------------------------------|-------------------------------------|--|

| S | CELU GOOT<br>Contraction<br>Contraction<br>Nord | Contraction Contraction Contraction |  |

|                            | GeorgiaTech<br>ISSCC'2012 | Kobe Univ.<br>ISSCC'2013        | This Work                        |

|----------------------------|---------------------------|---------------------------------|----------------------------------|

| Architecture               | Cache-on-CPU<br>Manycore  | Memory-on-Logic<br>1 layer DRAM | Logic-on-Logic<br>2 layers 3DNOC |

| Process &<br>3D technology | 130nm<br>F2F CuCu         | 90nm<br>F2B TSV                 | 65nm<br>F2B TSV                  |

| 3D Bandwidth               | 277 Mbps                  | 200 Mbps                        | 326 Mbps                         |

| 3D I/O Power               | -                         | 0.56 pJ/bit                     | 0.32 pJ/bit                      |

## • 3D Link Performances

- Fastest link, +20% (326 Mflit/s)

- Best Energy Efficiency, +40% (0.32 pJ/bit)

- Self-Adaptation to Temperature, a strong 3D concern

An efficient 3DPlug (asynchronous 3DNOC including test & fault tolerance): a first step towards 3D-based computing architectures

# **3D TECHNOLOGY & 3DNOC CIRCUIT**

MPSOC | CLERMIDY Fabien | July 11, 2016 | 8

×40.0

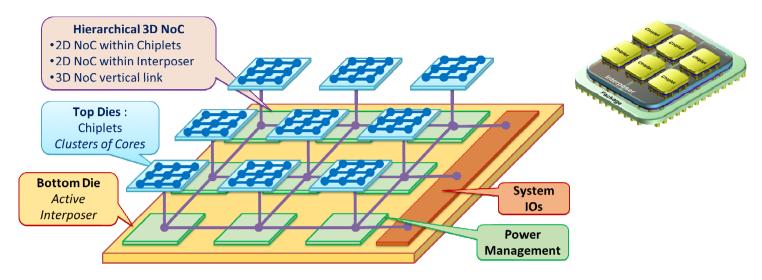

# **ACTIVE INTERPOSER PARTITIONING FOR MANY-CORE**

- « Active » Interposer : which added value ?

- Heterogeneous 3D

- System IOs

leti

Ceatech

Power Management

- Advanced tech node for computation within chiplets

- Mature tech node for communication/power/DFT/etc

- Chip-to-Chip Interconnect Hierarchical NoC, for energy efficient communications

- On Interposer, for off-chip memory accesses

- Chiplet power supply, without any external passives

- And most of all ... preserve (active) interposer cost with mature technology !

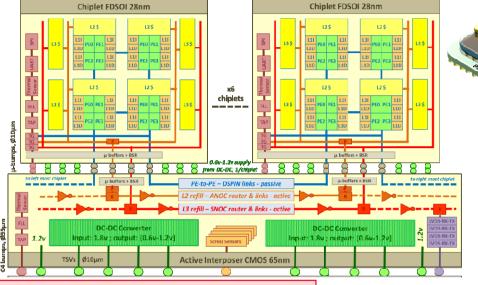

### INTACT : AN ACTIVE INTERPOSER IN ADVANCED 3D TECHNOLOGY FOR CACHE COHERENT MANY CORE

leti

ceatech

Active Interposer CMOS 65nm

#### **Many Core System**

- Clusters of MIPS32 cores (TSAR architecture)

- L1 \$ + L2 \$ + L3 \$ : fully cache coherent architecture

- 96 cores total, 100 GOPS/s, 34 MByte total cache, 25 Watt exp.

- Advanced Interconnect & clocking schemes

- Thermal Sensors, PVT Sensors, Mechanical Stress sensors

### Advanced 3D technology

- μ-bumps (10μm diameter, 20μm pitch)

- CuCu Hybrid Bonding (7 20 μm pitch)

- TSV middle (1:10 AR, 40µm pitch)

- Back Side RDL (10µm pitch)

- Large size interposer (200 mm2, with 22mm2 chiplets)

### **3D Partitionning**

- 6 Chiplets in Advanced 28nm FDSOI technology, with Body biasing

- Active interposer in 65nm CMOS, with « Smart features »

13 mm

- Integrated Power Management (Switch cap DC/DC converter)

- Pipelined NoC Interconnects + Fast IOs (LVDS links)

- **3D DFT infrastructure**

15 mm

IRT 3D Program

MPSOC | CLERMIDY Fabien | July 11, 2016 | 10

- SoC complexity is currently limiting the innovation

- 3D staking can give a new dynamic

- From IP reuse to chiplet reuse

- 3D technology basics are ready and technology is progressing quickly

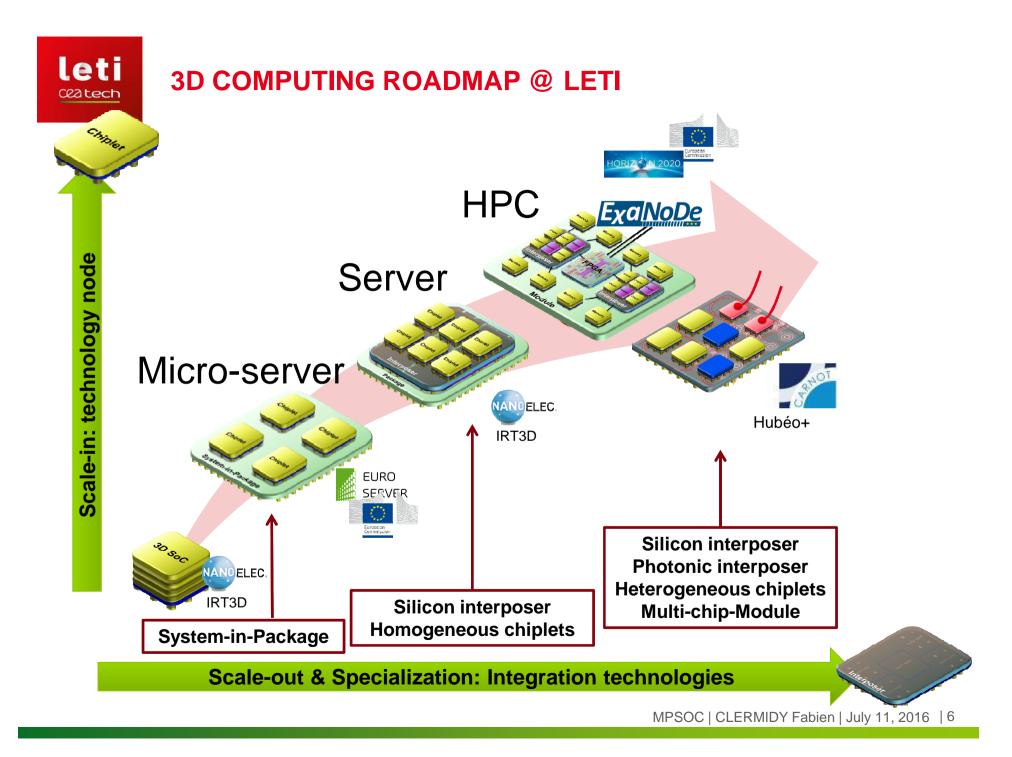

- Full LETI's roadmap for exploring this new world of possibilities

# THANK YOU FOR YOUR ATTENTION

**QUESTIONS?**