MPSoC 2017

Machine learning Based Intelligent Interconnect for Next Generation Autonomous Vehicle SoCs

Rocco Jonack

# Challenges Facing Autonomous Vehicles

## Translating System-Level Requirements → SoC Level

Exploding Performance Requirements

- Rise of heterogeneous architectures & right-sized compute

- Cache coherency & End-to-end QoS of critical importance

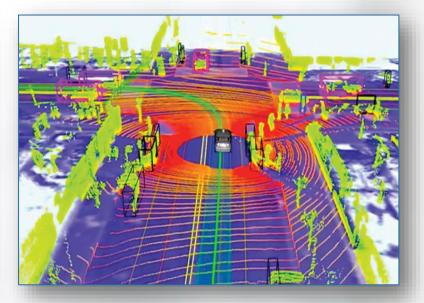

Real-Time Sensor Processing

- Different IPs with differing requirements

- ▲ Ensuring communication happens without any deadlocks

Ultra-High Safety & Reliability

- → Pressure to comply to industry standards ISO 26262

- **▲** Functional Safety Performance Area Tradeoffs

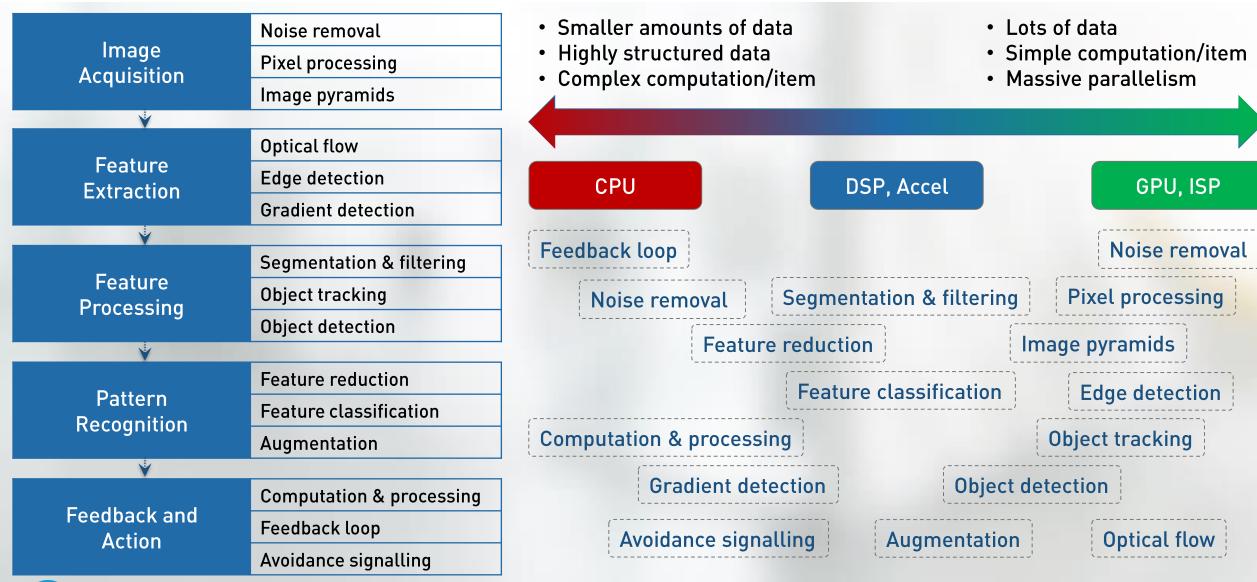

# **Autonomous Driving: Use Case Compute Flow**

Noise removal **Image** Pixel processing Acquisition Image pyramids Optical flow Feature **Edge detection** Extraction **Gradient detection** Segmentation & filtering **Feature** Object tracking **Processing Object detection** Feature reduction Pattern Feature classification Recognition Augmentation Computation & processing Feedback and Feedback loop Action Avoidance signalling

# **Need For Heterogeneous Computing**

## Challenges With Heterogeneous Computing

Cache Coherency Ensure every compute engine has uniform view of system memory

System-Level QoS BW-Hogs, Latency-sensitive & Real-time engines need seamless access to memory

End-to-End Functional Safety

Underlying architecture should be resilient & tolerant to random & systematic errors

- Smaller amounts of dataHighly structured data

- Complex computation/item

- Lots of data

- Simple computation/item

- Massive parallelism

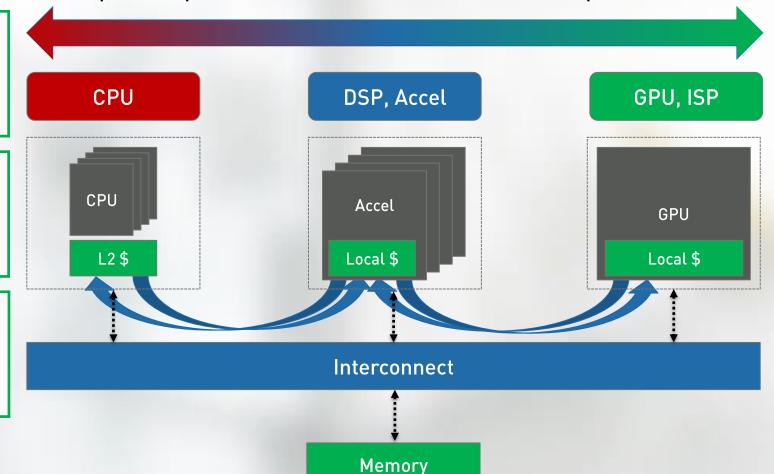

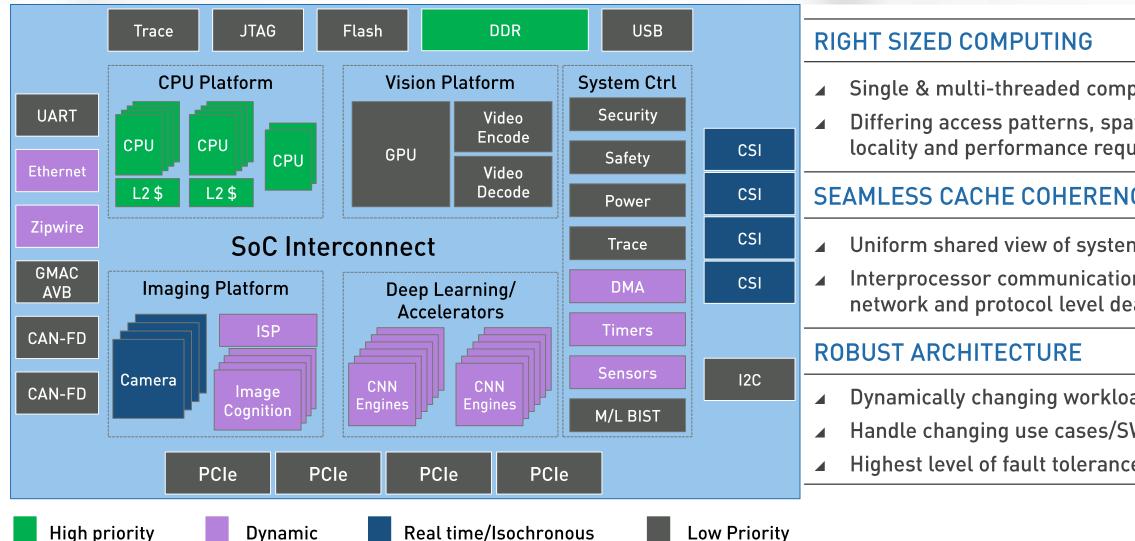

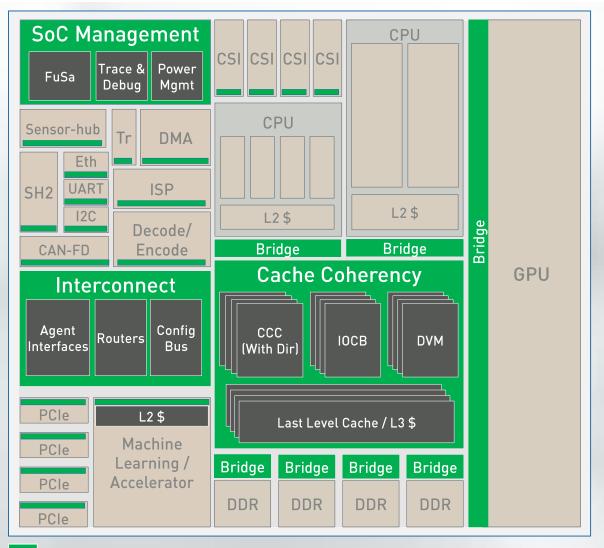

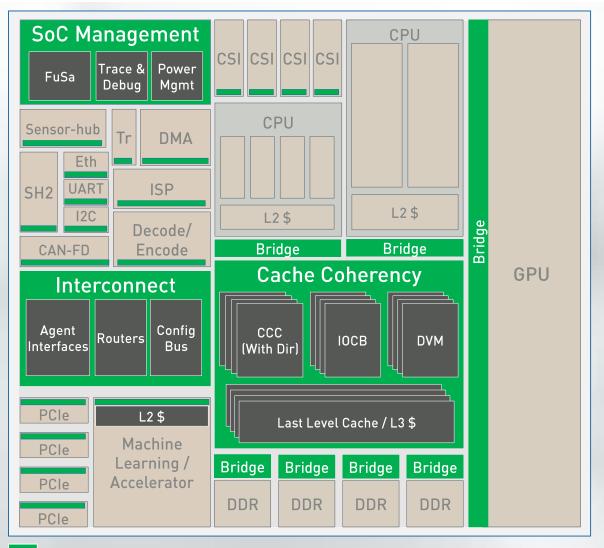

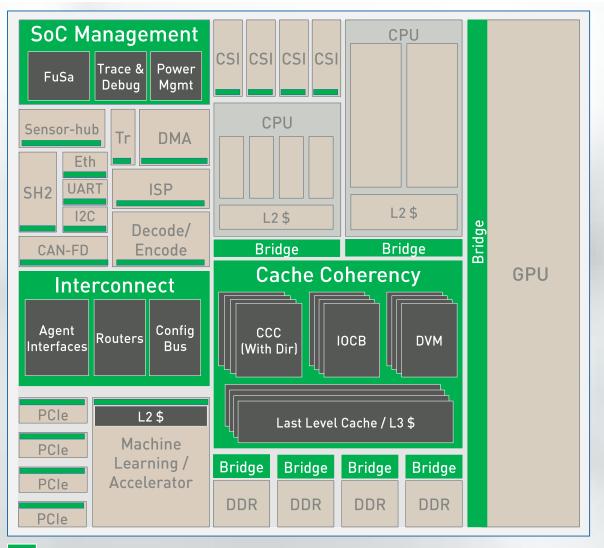

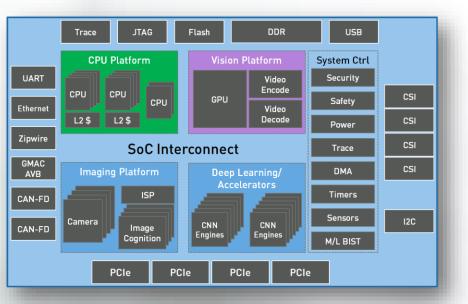

## Next-Gen Autonomous SoC Architecture Details

- Single & multi-threaded compute engines

- Differing access patterns, spatial/temporal locality and performance requirements

#### SEAMLESS CACHE COHERENCY

- Uniform shared view of system memory

- Interprocessor communications lead to network and protocol level deadlocks

- Dynamically changing workloads

- Handle changing use cases/SW needs

- Highest level of fault tolerance

## **Existing Approaches Fall Short**

### Hard, Fixed Point Designs

- Fixed topology with limited configurability

- Coherency through "tiled" structures and regular connection patterns

### Manual, Hand-optimized

- Hand-optimized sub systems

- Divide and conquer approach: Separate coherent, non-coherent

- ▲ Deadlock prone designs

### **Key Elements Are Afterthoughts**

- QoS schemes are patched, built on top of existing infrastructure

- ✓ Functional safety features is "added-on" instead of being architected in the solution

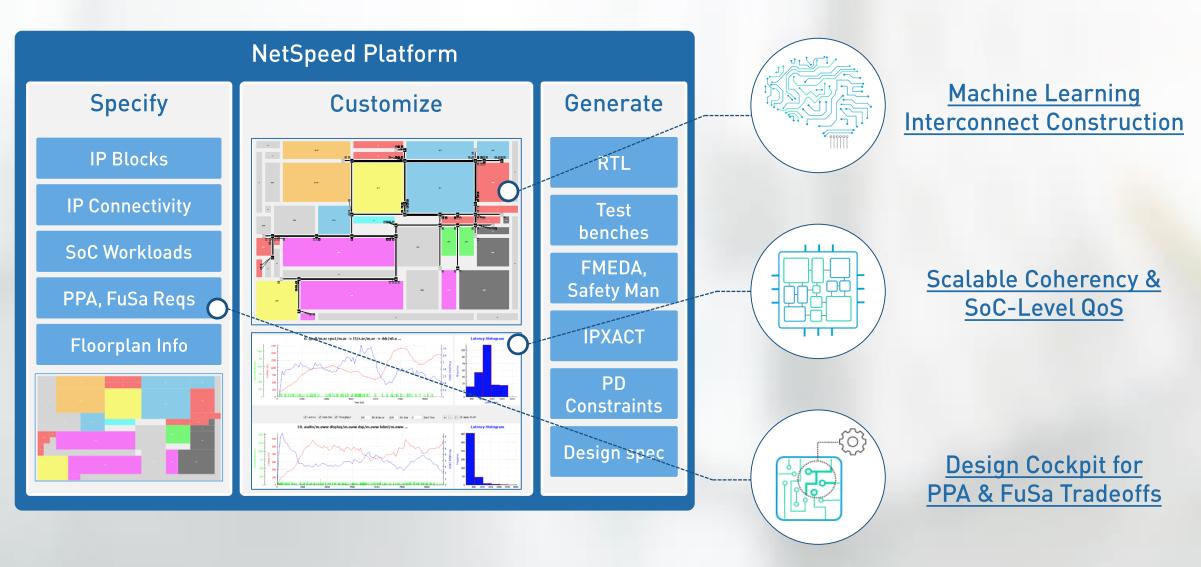

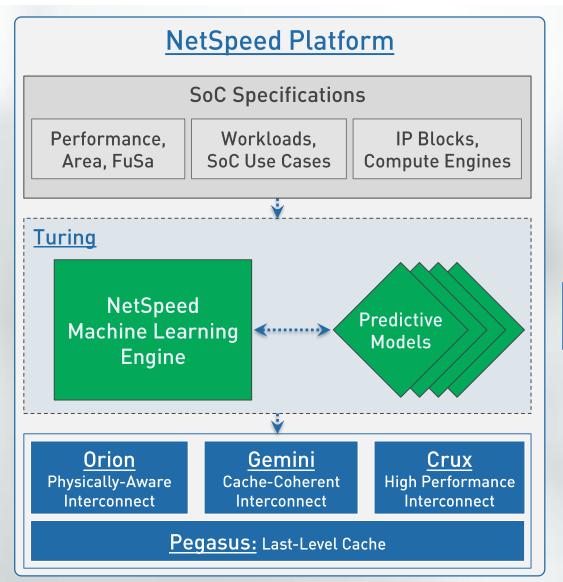

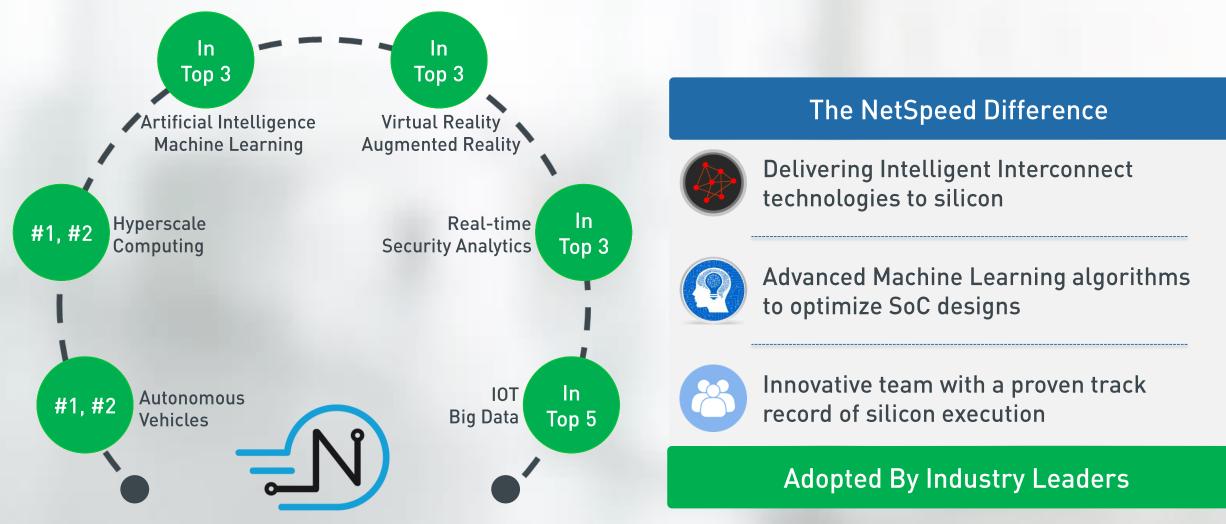

## NetSpeed Technology: Intelligent Interconnect Architecture

# Machine Learning Based Interconnect Construction

## Scalable Cache Coherent Interconnect

### Configurable Cache Coherency

- ▲ Scalable coherency solution: Modular & programmable

- ▲ In-built directory support

- ▲ Specialized IO-Coherency accelerator

### Multi-Level Caching Options

- ▲ Programmable allocation policies

#### Scalable Solution

- ▲ 64 cache coherent cluster; 250 IO coherent IPs

- ▲ Seamless connection with DDR, HBM memories

- ▲ In-built deadlock detection and avoidance

NetSpeed Gemini Components

## Scalable Cache Coherent Interconnect: Built-In Deadlock Avoidance

#### **Built-In Deadlock Detection & Avoidance**

- ▲ Formal methods and graph theory algorithms

- User-driven traffic dependencies

- ▲ Handles complex topologies and routing

NetSpeed Gemini Components

## Advanced SoC-Level QoS Schemes

#### **Dynamic QoS Control**

- ▲ 16 Traffic Classes & 64 Virtual Channels with Dynamic priority

- ▲ Low-latency QoS control for Isochronous traffic flows

#### **End-to-End QoS**

- ▲ Improved, lower-latency flow-control with memory scheduler

- ▲ Non head-of-line blocking schemes with guaranteed delivery

### Runtime Programmability

- ▲ Runtime programmable weighted BW allocation

- ▲ Adaptive control to DVFS modes without software intervention

NetSpeed Gemini Components

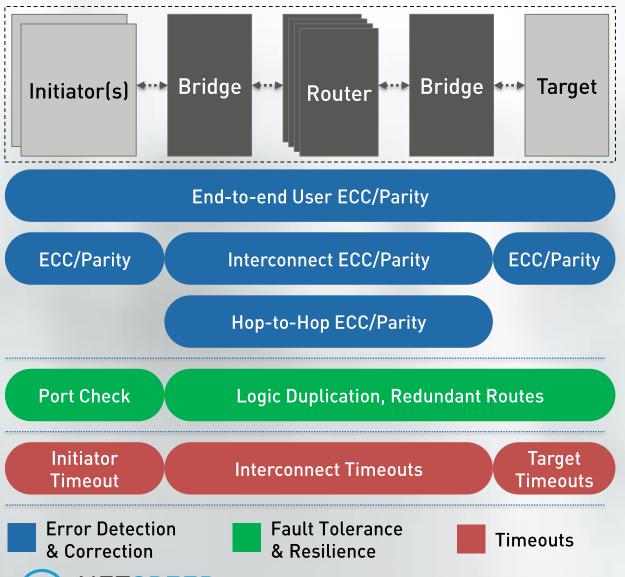

## Functional Safety: ISO 26262 ASIL-D

### FuSa Architected In With Top-Down Approach

- ▲ FuSa features considered first class citizens from Day #1

- ▲ Interplays cleanly with coherency and ISO 26262 standard

- ▲ End-to-end protection, logic redundancy & timeouts

### Unprecedented Configurability

- ▲ Fine grained FuSa feature control for low area overhead

- Design cockpit for Performance vs. FuSa vs. area tradeoffs

- ▲ Rapid analysis and convergence

#### **ASIL-D Ready**

- → First & Only Coherent Interconnect IP

- Detailed FMEDA analysis & reporting for any configuration

- ▲ Comprehensive Safety Manual & Safety Report

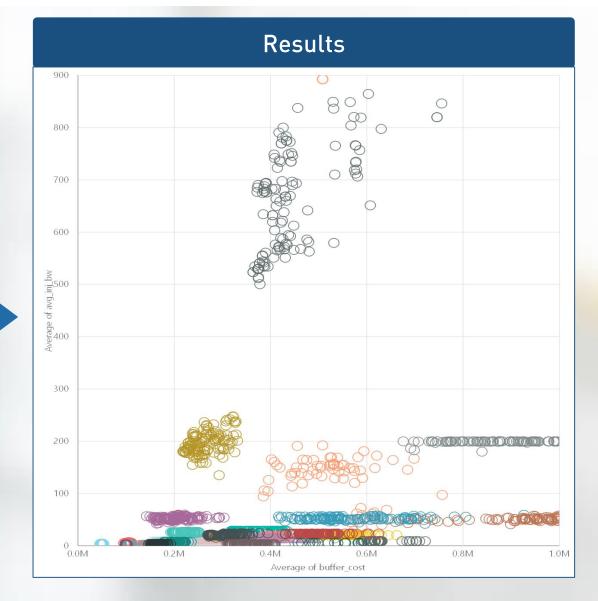

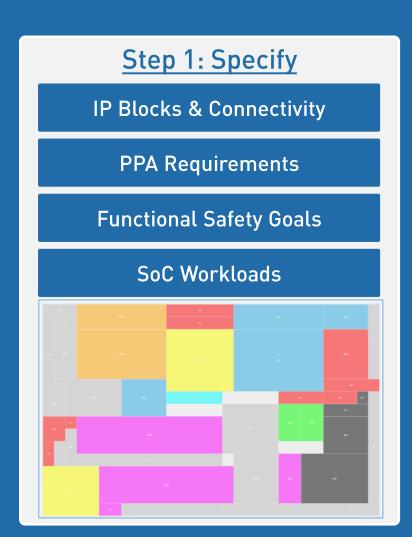

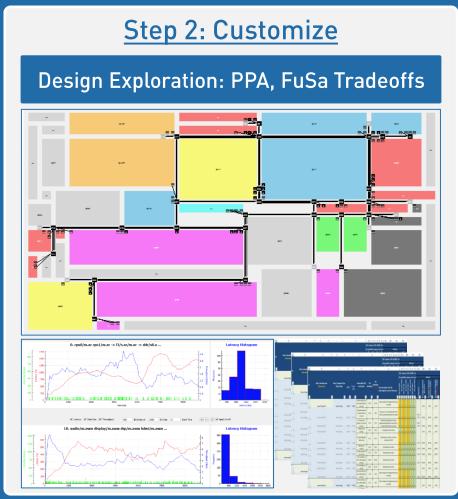

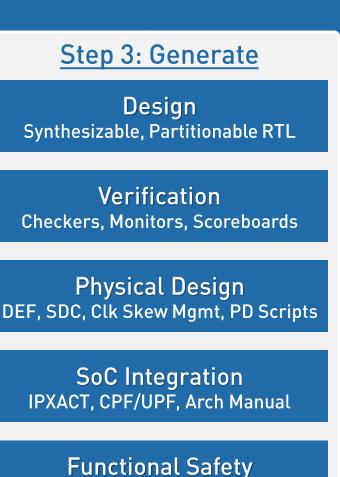

# Design Cockpit: Balancing Performance vs. Area vs. FuSa

### NetSpeed Design Cockpit

FMEDA, Safety Manual

## **Customer Case Study**

#### Customer

- <u>Tier #1</u> Automotive manufacturer and Tier #1 ADAS company

- Architecture and frontend design by customer

- Back-end by 3<sup>rd</sup> party ASIC vendor

### Challenge

- Many clusters of CPUs and proprietary accelerators requiring <u>high-bandwidth</u>, <u>low latency</u>, distributed <u>coherent interconnect</u>.

- No other solution in the market has <u>Robust Real-time QoS</u> support

- Reliability and safety features for ADAS market

#### Solution

- Scalable Gemini performance far exceeds competing interconnect capabilities

- <u>User-controlled automation</u> with integrated performance analysis allows architect to tune

Bandwidth/latency/area tradeoffs for specific traffic flows

- Functional safety architected into interconnect, configured on a per-traffic-flow granularity

# **Customer Case Study**

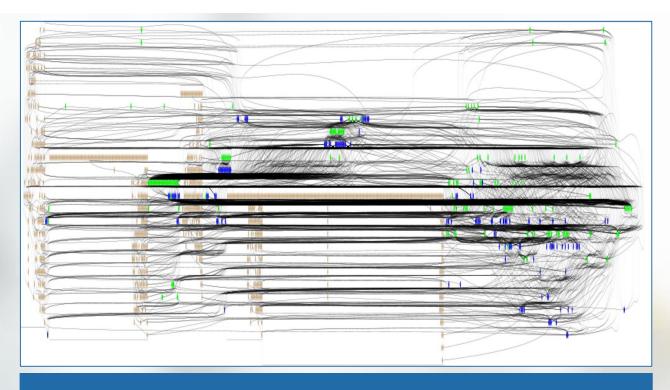

### **Performance** Coherency → Configurable Coherency Latency → 30% lower Bandwidth → 20% higher @ saturation → ASIL-D FuSa **Design Time** Timing closure → First time timing clean through P&R Wires -> Reduced congestion seen during layout → Automatically inserted by physical aware flow Buffers Other Customizable → Functional safety levels tailored to traffic flow Start-Finish → 9 months

## NetSpeed Technology: Choice of Next-Gen Application Leaders

**NetSpeed Systems**

## Summary

#### HETEROGENEOUS ARCHITECTURES

Cache coherency critical for delivering high performance

#### **NETSPEED TECHNOLOGY**

■ Scalable coherency solution with uniform view of system memory

#### REALTIME SENSOR PROCESSING

▲ Complex IP interactions needing sophisticated QoS schemes

#### **NETSPEED TECHNOLOGY**

▲ Advanced QoS schemes with traffic isolation & BW allocation

#### **SAFETY & RELIABILITY**

▲ Functional Safety needs to be architected, not added-on

#### NETSPEED TECHNOLOGY

▲ ASIL-D Ready: Robust safety mechanisms architected in IP