# How we design AI accelerator SoC for Data Center Network

MPSoC2024 Kishishita Keisuke kishishita.keisuke@socionext.com Socionext

## Socionext

Founded in 2015

IPO in 2022

1900+ Engineers, many of 20+ years experts

Offices Japan(HQ)/US/EU/China/Taiwan/India/Korea

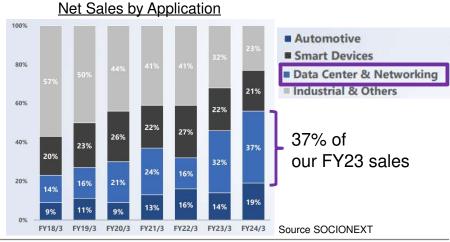

## Focus segment

#### **Data Center & Networking**

#### Multi Core CPU

Al Accelerator

<u>5G</u> Wireless

Wired Network

**Storage**

<u>Optical</u> Transporter

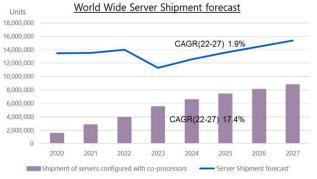

The market of server with co-processor is a growing market for CAGR(22-27) 17.4%

Created by SOCIONEXT based on OMDIA Long range server forecast -2H23

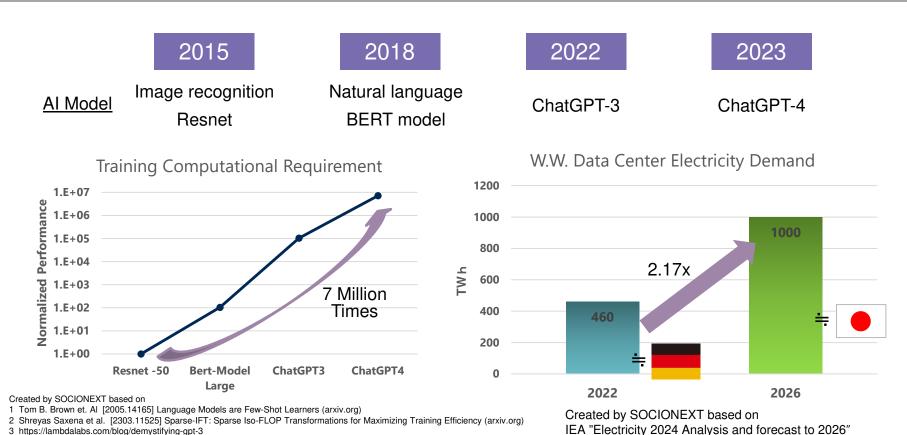

## Power consumption issues due to the spread of Al

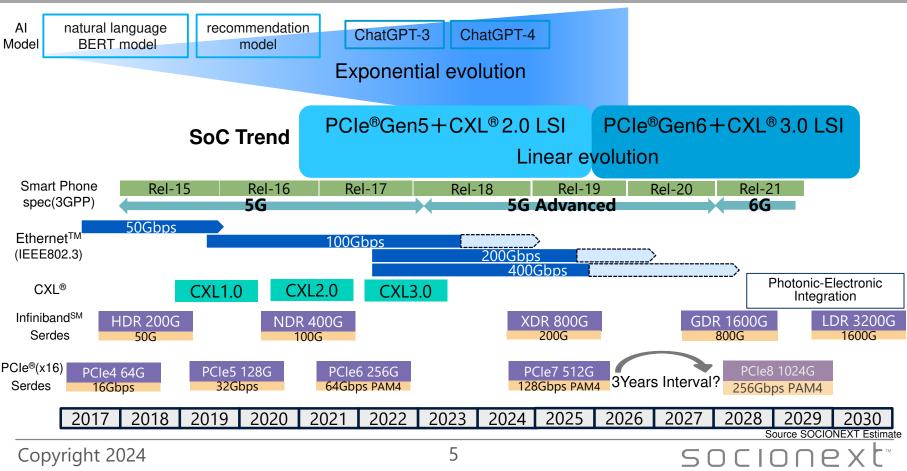

# AI & Network Trend

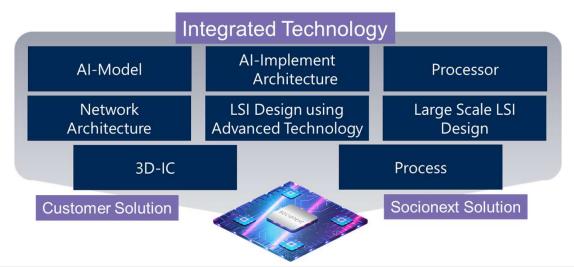

## Integrated Technology for AI accelerator

## Symphony of technological breakthroughs

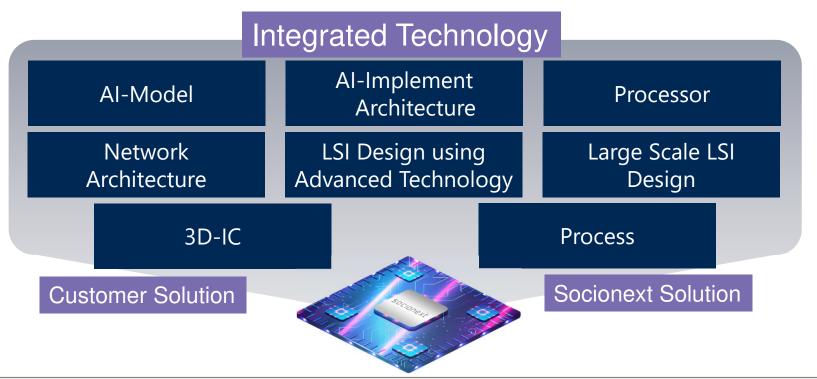

# Socionext Integrated Technology

Integrated Technology Socionext Solution ✓ Advanced Package Solution Large Scale LSI Design ✓ Chiplet Design ✓ Multi-Core CPU **Processor** LSI Design using ✓ Clock latency reduction structure Advanced Technology

## Advanced Package Solution

### Chiplet Package Experiences

|            | Device-1                | Device-2                                             | Device-3                                | Device-4                                       |

|------------|-------------------------|------------------------------------------------------|-----------------------------------------|------------------------------------------------|

| Appearance |                         |                                                      |                                         |                                                |

| Structure  | 2x SoC Die<br>Capacitor | 1x SoC Die<br>4x HBM2E<br>Si interposer w/ capacitor | 1x SoC Die<br>4x HBM2E<br>Si interposer | 4x SoC Die<br>4x HBM3<br>Bridge/RDL interposer |

| Package    | MCM-FCBGA               | 2.5D-FCBGA                                           | 2.5D-FCBGA                              | 2.5D-FCBGA                                     |

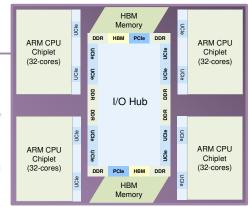

## Multi-Core CPU Chiplet

- Collaboration with Arm and TSMC on 2nm Multi-Core CPU Chiplet

Press Release

#### Socionext Announces Collaboration with Arm and TSMC on 2nm Multi-Core Leading CPU Chiplet Development

Next-Generation Compute Chiplet-based Proof-of-Concept Leverages Arm Neoverse

CSS Technology and TSMC Silicon Process Along with Advanced Packaging Technology

[Yokohama, Japan October 18, 2023] --- Socionext today announced a collaboration with Arm and TSMC for the development of an innovative power-optimized 32-core CPU chiplet in TSMC's 2nm silicon technology, delivering scalable performance for hyperscale data center server, 5/6G infrastructure, DPU and edge-of-network markets.

This advanced CPU chiplet proof-of-concept using Arm® Neoverse™ CSS technology is designed for single or multiple instantiations within a single package, along with IO and application-specific custom chiplets to optimize performance for a variety of end applications.

Leveraging CPU chiplets, and customized application-specific chiplets, multiple target applications can be supported. When new chiplets become available, a cost-effective package level upgrade path can be supported.

128 CPU core HPC Soc(Image)

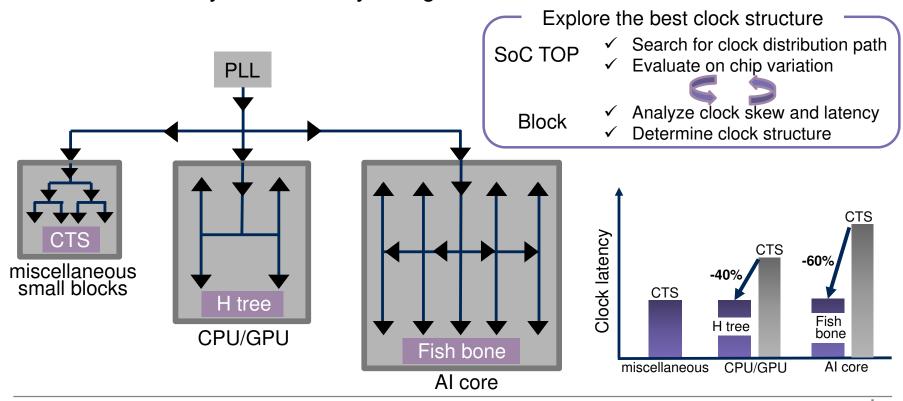

## Clock latency reduction structure

#### Minimize latency and skew by using three different clock structures

SOCION

## Summary

- ✓ Data center semiconductors will continue to drive technology.

- ✓ On the other hand, it is also a factor contributing to the global power challenge.

- ✓ Socionext aims to balance technology evolution and power challenges with Integrated Technology.