#### Fine grain DVFS power-aware control

E. Beigné, I. Miro, Y. Thonnart, P. Vivet, S. Lesecq, D. Pushini, F. Tabet, K. Benchehida, R. David, O. Heron, C. Bour, L. Alacoque, A. Peizerat

MPSoC 2011, Beaune

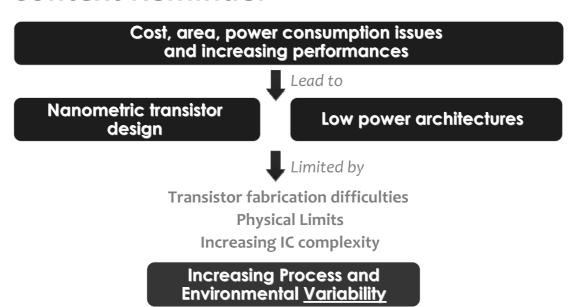

- Objective An Adaptive Voltage and Frequency scaling approach at fine grain to reach a functional optimal energetic point according to PVT variations

- Context Reminder

- GALS NoC Architectures

- Adaptive Architectures

- MPSoC fine-grain power control

- Our Fine-grain AVFS proposal

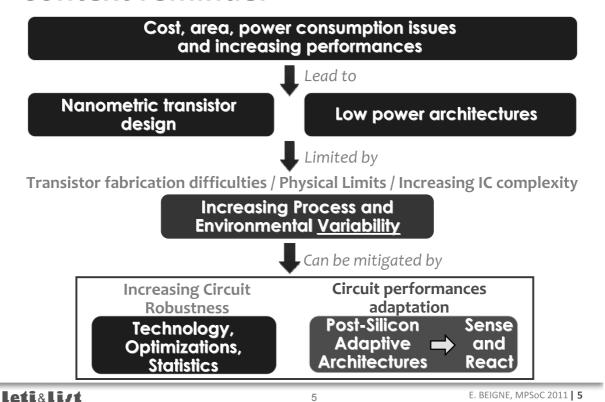

#### **Context Reminder**

Leti&li/t

8. BEIGNE, MPSoC 2011 | 3

#### **Context Reminder**

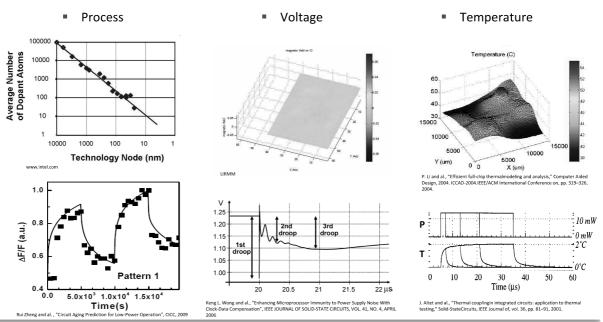

PVT variations with very different spatial and temporal dynamics

#### **Context reminder**

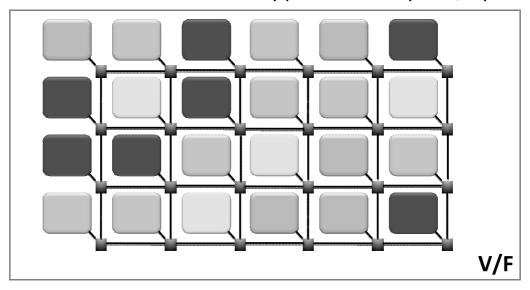

#### **GALS NoC architectures**

- Main innovations based on <u>GALS</u> architectures (Globally Asynchronous and Locally Synchronous NoC since 2002

- Based on a strong knowledge on asynchronous QDI circuits

- A <u>basic architecture</u> for a simple, efficient and low power clock distribution

- A natural enabler for a fine grain dynamic power management :

- Easy frequency scaling (independant frequency islands)

- Fine grain voltage and Vt management (independant voltage and frequency islands)

- An <u>essential architecture</u> for PVT variations to avoid worst case design :

- Fine grain adaptive architecture (local V/F point adapted to dynamic PVT variations)

- Asynchronous QDI robustness to variations

- => One unique target : Reach an optimum functionnal point at a maximum speed for a minimum energy considering local, global and environmental variations

leti&li/t

#### **Adaptive architectures**

- A dynamic adaptive architecture to allow circuit performances regulation :

- Improve circuit performance (power, speed)

- Improve the yield

- We need to :

- Know the real process corner case

- Dynamically follow the temperature, voltage and aging evolution

- ⇒ Find an **optimum functional point** avoiding important design margins

leti&list

E. BEIGNE, MPSoC 2011 | 7

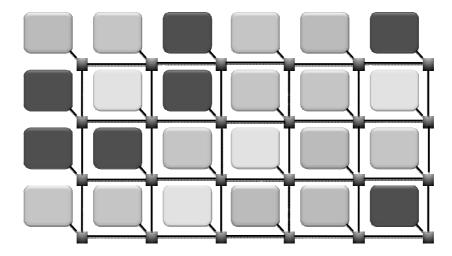

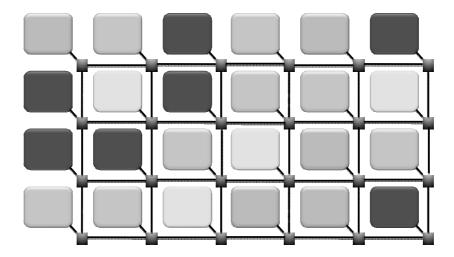

## MPSoC fine-grain power control

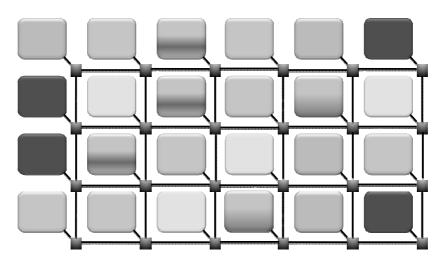

On-chip Process variations

## **MPSoC fine-grain power control**

Dynamic PVT evolution

leti&li/t

E. BEIGNE, MPSoC 2011 | 9

## MPSoC fine-grain power control

Unbalanced workload according to application

## MPSoC fine-grain power control

What about a worst case approach : unique V/F point ?

leti&li/t

E. BEIGNE, MPSoC 2011 | 11

# MPSoC fine-grain power controlAdpative fine grain approach for maximum energy

Adpative fine grain approach for maximum energy gain and efficiency

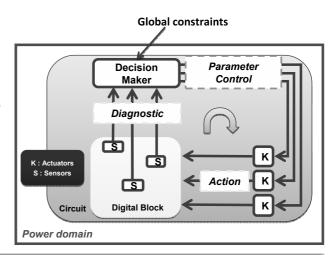

## **Adaptive architecture**

#### **Hardware platform considered:**

- LoCoMoTIV\* hardware platform developed by CEA-LETI Minatec

- A 32nm STMicroelectronics technology demonstrator for fine grain Local Dynamic Adaptive Voltage and Frequency Scaling

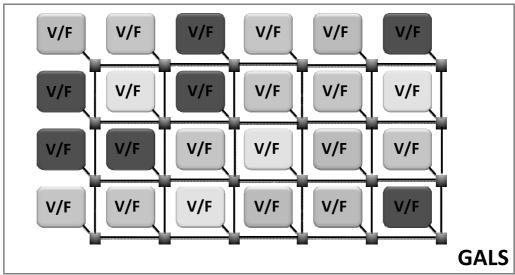

- GALS Architecture

- Sense and React architecture :

- Sensors

- Process-Voltage-Temperature

- Timing fault

- Actuators

- Local supply voltage generation (V) using Vdd-hopping

- Local clock generation (F) using low area FLL

- Power/Variability Control

- Local control with minimum hardware

- Global control : high level algorithms

E. Beigné and H. Metras, "A Dynamically adaptive multiprocessor architecture addressing advanced CMOS technology variability", ESC conference, May 2-5 2011

\* Local Compensation of Modern Technology Induced Variability

leti&list

E. BEIGNE, MPSoC 2011 | 13

© CEA. All rights reserved

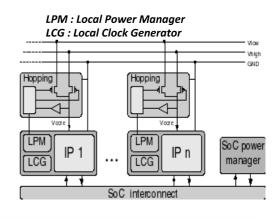

#### **Domains main characteristics**

- Each domain is an independent power and frequency domain:

- a GALS scheme within the cluster

- domains are synchronous islands using programmable clock generator

- Within each domain, the logic core is supplied by *Vcore* voltage generated from the external available voltages:

Vhigh/Vmedium/Vlow/Vdrowsy

- Dynamic variability monitoring

- Local fine grain power and variability management can be executed during IP computation and communication independently from the others

leti&li/t

E. BEIGNE, MPSoC 2011 | **14**

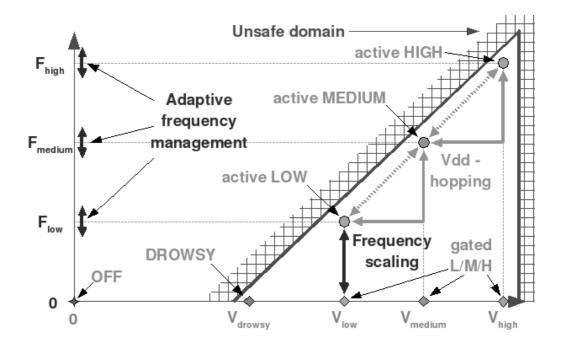

#### Power domain 'power modes'

Leti&Li/t E. BEIGNE, MPSoC 2011 | 15

## **Area/Power/performance budget**

- Considering a Power Domain of about 0,75 mm² in 32 nm running at 600 MHz

- For an area overhead of ~10% we can obtain from 20% to 80% of dynamic power consumption reduction depending on :

- Intrinsic variability

- Workload balancing

- Allow to find a functionnal point (V/F) even at low speed whatever is the process variation

leti&li/t

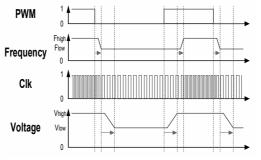

## Actuators Vdd Hopping Power Supply Unit

- Power Supply Unit manages internal Vcore :

- Two fixed voltages available : Vhigh/Vlow

- Hop between those two values using a dithering ratio

- Two power switches Thigh and Tlow LVT transistors

- A Hopping Unit (for fine grain AVFS at IP level)