17th INTERNATIONAL FORUM ON MPSoC

for software-defined hardware

Speaker's Profile

Abstract

Persistent memory places NVRAM on the memory bus, offering fast access to persistent data. Yet maintaining NVRAM data persistence raises a host of challenges. Most previous designs either incur much performance overhead or require substantial modifications to existing architectures. I will present a persistent memory accelerator design, which guarantees NVRAM data persistence by hardware yet leaving cache hierarchy and memory controller operations unaltered. A nonvolatile transaction cache keeps an alternative version of data updates side-by-side with the cache hierarchy and paves a new persistent path without affecting original processor execution path. As a result, our design achieves the performance close to the one without persistence guarantee.

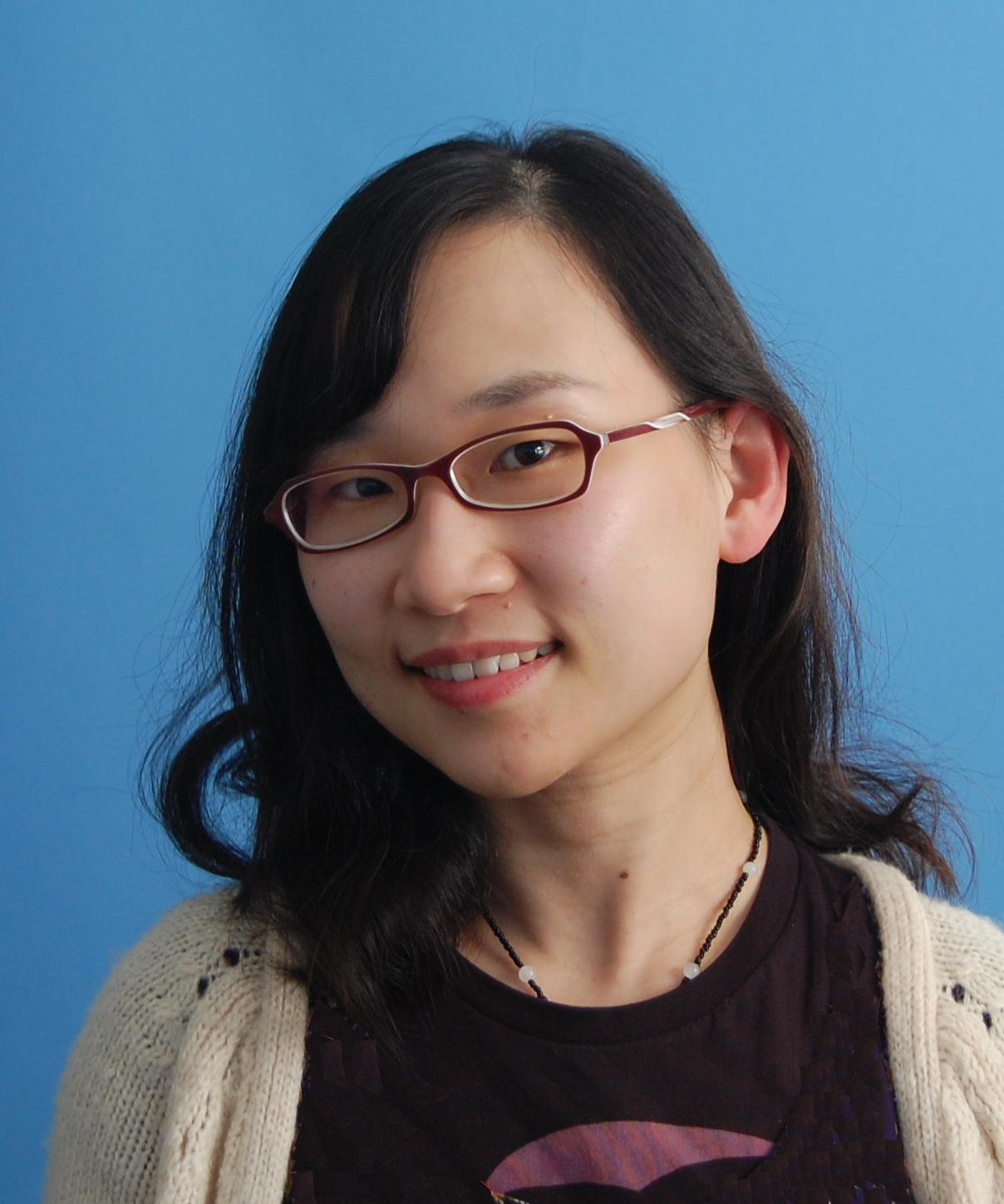

Biography

Jishen Zhao an Assistant Professor at Computer Engineering Department of University of California, Santa Cruz. Before joining UCSC, she was a Research Scientist at HP Labs. Her research spans and stretches the boundary between computer architecture and system software, with a particular emphasis on memory and storage systems, domain-specific acceleration,, and high-performance computing. Her research is driven by both emerging device/circuit technologies (e.g., 3D integration, nonvolatile memories) and modern applications (e.g., big-data analytics, machine learning, and scientific computing).