17th INTERNATIONAL FORUM ON MPSoC

for software-defined hardware

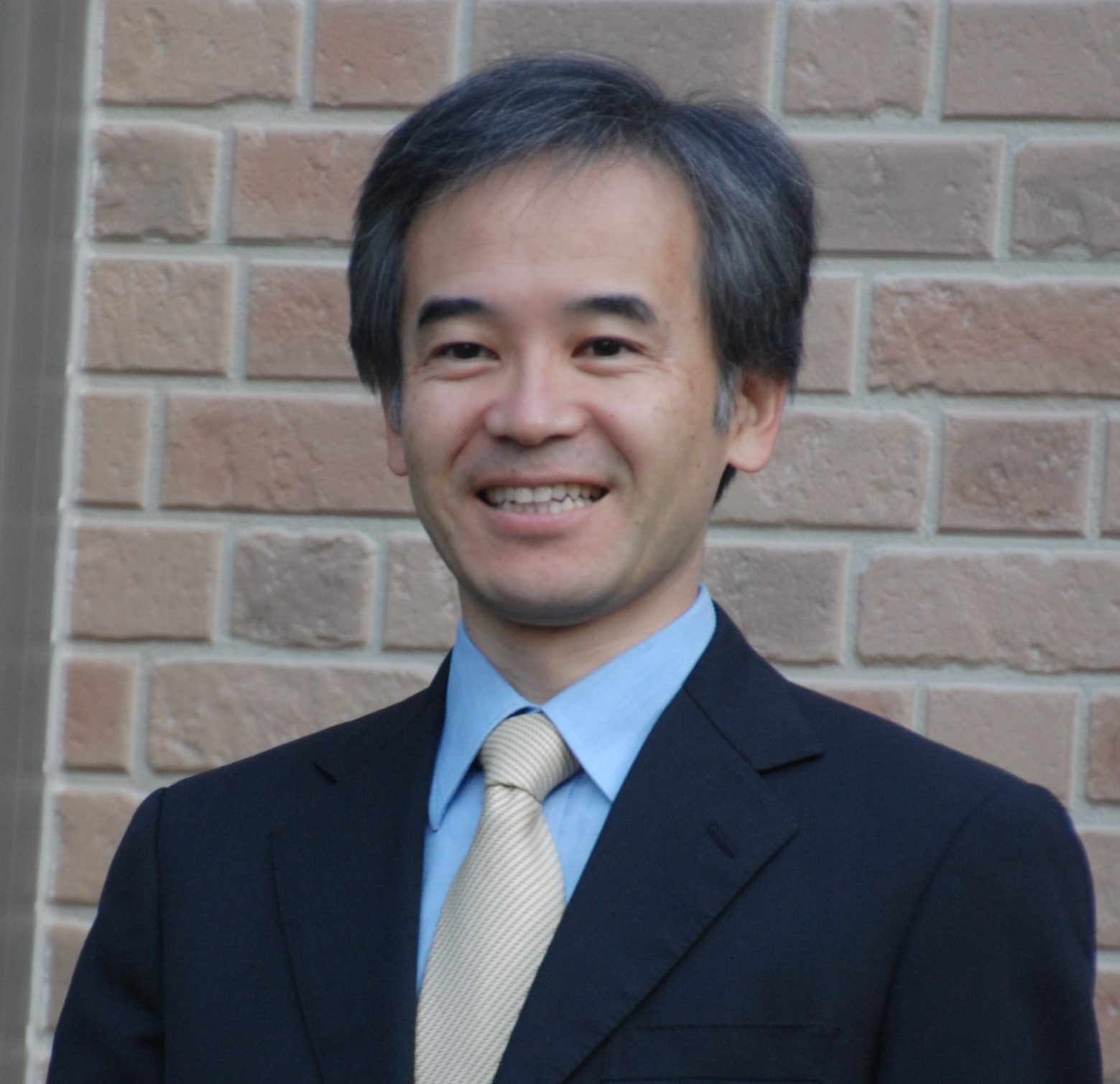

Speaker's Profile

Shintaro Yamamichi

IBM Research-Tokyo, Japan

Neuromorphic hardware research for Cognitive Computing

Abstract

Despite many drastic improvements in image and speech recognition by sophisticated machine learning techniques, such as deep learning, a completely new hardware based on a non-Von Neumann architecture is becoming crucial in terms of low power consumption in the order of several magnitudes. Many neuromorphic devices mimicking the signal operation in human brains have been recently reported. The SRAM-based device operated with a spiking neural network is an example, and achieves the power consumption of almost thousand times smaller than that of the conventional microprocessors in image recognition. In addition, a cross-bar array structure neuromorphic device realizes on-chip leaning and high-density synaptic functions in a small footprint. Also, not just a neuromorphic device itself, but off-chip interconnect technology is playing a very important role to realize sophisticated system using neuromorphic devices.

In this talk, new research trends for these neuromorphic hardware will be reviewed, in addition to showing the concept of Cognitive Computing, which we believe will be the best computing platform in the Big Data era.

Biography

Shintaro Yamamichi received his B.E., M.E. and Ph. D. degrees in electrical engineering, from Kyoto University, Japan, in 1987, 1989, and 2002, respectively. He was involved in both semiconductor and packaging process research in Japanese semiconductor companies, and was a visiting industrial fellow at University of California, Berkeley, in 1997. In 2013, he joined IBM Research -Tokyo, working on the research planning for future hardware in the Cognitive Computing era. Since 2016, he has been the senior manager of Science & Technology, IBM Research -Tokyo, leading the neuromorphic hardware research agenda.