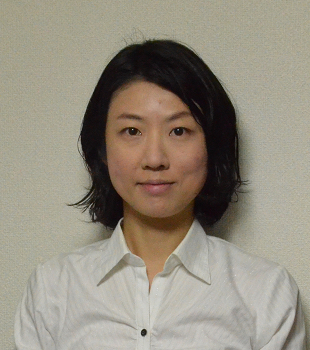

Yuko Hara-Azumi

Tokyo Institute of Technology, Japan

Highly-Scalable and Flexible Multicore Processors with Limited ISAs

Abstract

Reducing energy consumption and keeping high applicability to a variety of applications are contradicting design requirements but both essential for embedded computing devices, especially in the IoT era. Contrary to most embedded processors that are getting richer resources for higher performance, we propose multicore processors whose cores individually possess minimum resources by limited ISAs. Our multicore processors design enables the flexible customization in the number of processor cores and inter-core communication depending on the applications and design constraints. This is done through template-base customization, in order to provide both good design-productivity and scalability. The goal of our work is to enhance energy-efficiency of multicore processors by minimizing the energy-waste through the use of the tiny processor core. This talk demonstrates some case studies to show the effectiveness of our processors in terms of scalability and flexibility.

Biography

Yuko Hara-Azumi received her Ph.D. degree in information science from Nagoya University in 2010. She was a JSPS postdoctoral research fellow at Ritsumeikan University from 2010 to 2012, during which she was also a visiting scholar at University of California, Irvine, USA and Karlsruhe Institute of Technology, Germany. In 2012, she joined Nara Institute of Science and Technology as an assistant professor. Since 2014, she has been with Tokyo Institute of Technology, where she is currently an associate professor. Her research interests include system-level design automation, especially on high-level and logic synthesis and hardware/software co-design, for embedded/dependable systems. She currently serves as organizing and program committees of several premier conferences including DAC, ICCAD, DATE, ASP-DAC, FPL, and so on.